À l'intérieur du NVIDIA Blackwell Ultra : la puce qui propulse l'ère des usines d'IA

Sources: https://developer.nvidia.com/blog/inside-nvidia-blackwell-ultra-the-chip-powering-the-ai-factory-era, https://developer.nvidia.com/blog/inside-nvidia-blackwell-ultra-the-chip-powering-the-ai-factory-era/, NVIDIA Dev Blog

Aperçu

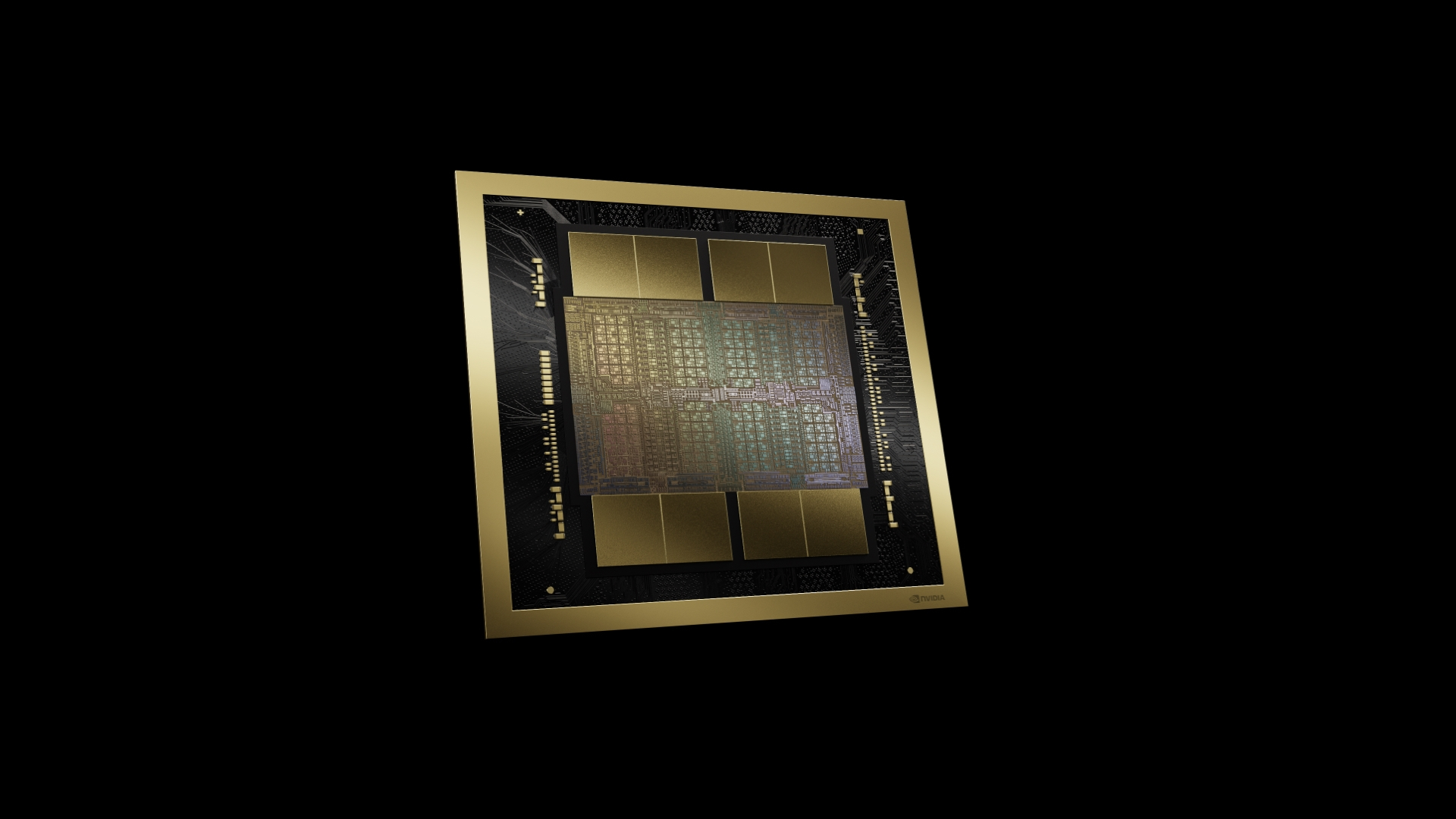

NVIDIA Blackwell Ultra représente le dernier membre de la famille d’architectures Blackwell, conçu pour accélérer l’entraînement et le raisonnement en IA à l’échelle. Il fusionne des innovations en silicium avec une intégration système plus poussée, offrant performance, scalabilité et efficacité pour les usines IA et les services IA en temps réel qu’elles alimentent. L’efficacité énergétique est au cœur du design, avec une architecture à double reticle, une mémoire à large bande passante et de grande capacité (HBM3e), des Tensor Cores de cinquième génération et un format de précision NVFP4 4 bits. Le Blackwell Ultra demeure un accélérateur CUDA‑programmable, conservant le modèle de programmation CUDA familier tout en apportant des gains mesurables pour les charges de travail denses et creuses. Ultra est composé de deux dies de taille reticle connectés par l’interface NV‑HBI, un interconnect die‑to‑die propriétaire et économe en énergie, qui fournit jusqu’à 10 TB/s de bande passante. Fabriqué sur le procédé TSMC 4NP, Blackwell Ultra comporte 208 milliards de transistors — environ 2,6× ceux du Hopper (H100) — tout en conservant le fonctionnement comme un seul accélérateur CUDA‑programmable. L’implémentation complète comprend 160 Streaming Multiprocessors (SMs) organisés en huit Graphics Processing Clusters (GPCs). Chaque SM est une unité de calcul autonome incluant quatre Tensor Cores, soit 640 Tensor Cores au total sur la puce, désormais compatibles avec la précision NVFP4 et les capacités de la cinquième génération de Tensor Core. Chaque SM est associé à 256 KB de Tensor Memory (TMEM), conçu pour minimiser les déplacements de données et garder les opérandes près des unités de calcul. La plateforme supporte aussi le MMA à double thread-block, permettant à des SMs jumelés de coopérer sur une même opération MMA et de partager les opérandes, réduisant ainsi le trafic mémoire et améliorant l’efficacité. NVFP4 est le format FP‑float 4 bits de NVIDIA qui combine une échelle micro‑bloc FP8 (appliquée à des blocs de 16 valeurs) avec une échelle FP32 au niveau tensoriel. Ce format permet une quantification accélérée par matériel avec des marges d’erreur nettement plus faibles que le FP4 conventionnel. En pratique, NVFP4 peut offrir une précision proche de FP8 dans de nombreuses charges de travail IA tout en réduisant l’empreinte mémoire d’environ 1,8× par rapport au FP8 et jusqu’à ~3,5× par rapport au FP16. La capacité de calcul NVFP4 sur Blackwell Ultra offre un gain de performance et d’efficacité mémoire substantiel, particulièrement utile pour l’inférence en faible précision et le pré‑entraînement sur de grands lots. La variante Ultra porte les performances NVFP4 à environ 15 petaFLOPS, contre environ 10 petaFLOPS pour le Blackwell de base. L’architecture conserve le modèle de programmation CUDA, assurant que les développeurs puissent exploiter l’écosystème CUDA tout en bénéficient des performances accrues et de l’élargissement mémoire. Blackwell Ultra comprend 288 Go de mémoire HBM3e par GPU — une capacité qui est 3,6× supérieure à la mémoire embarquée du H100 et environ 50% supérieure à celle du Blackwell — conçue pour accueillir des modèles trillions de paramètres, étendre les fenêtres de contexte et permettre une inférence à haute concurrence sans offloading intensif du KV‑cache. Au‑delà du calcul, l’architecture introduit des moteurs spécialisés pour les workloads IA modernes traitant des données multimodales. le Transformer Engine de cinquième génération et les Tensor Cores de cinquième génération offrent un débit plus élevé et une latence plus faible pour les workloads denses et creux. Le traitement de l’attention, crucial pour les transformers à longues fenêtres de contexte, bénéficie d’un doublement du débit SFU pour les instructions clés d’attention, permettant une inférence de couche d’attention jusqu’à 2× plus rapide que sur Blackwell. Lorsque ces gains de performance se combinent avec la précision NVFP4 et la mémoire élargie, les résultats se traduisent par des améliorations de l’inférence à grande échelle et des workloads multi‑modales. Une caractéristique déterminante du Blackwell Ultra est sa mémoire intégrée et sa stratégie d’interconnexion. Chaque GPU dispose de 288 Go de HBM3e, permettant des fragments de modèle plus importants et des fenêtres de contexte plus largas dans un seul appareil. La plateforme prend en charge NVLink de cinquième génération pour la communication entre GPUs, NVLink‑C2C pour une interconnexion cohérente avec une NVIDIA Grace CPU et une interface PCIe Gen 6 x16 pour la connectivité avec l’hôte. L’alliance de ces interconnexions, de la mémoire et du calcul permet de dimensionner des usines IA et de connecter à l’écosystème Grace, assurant un flux de données à haut débit et une faible latence entre les composants. Dans le cadre système, Blackwell Ultra est conçu pour se placer au cœur des architectures d’usines IA de prochaine génération. Dans les configurations Grace‑Blackwell Ultra, un seul processeur Grace peut être associé à deux GPU Blackwell Ultra via NVLink‑C2C, offrant jusqu’à 30 PFLOPS de calcul dense et 40 PFLOPS de calcul sparse NVFP4. Ce Superchip peut être intégré dans le système GB300 NVL72, avec 1 To de mémoire unifiée combinant HBM3e et LPDDR5X pour une capacité on‑node sans précédent. ConnectX‑8 SuperNICs assure 800 Go/s de connectivité réseau, facilitant l’entrée et la sortie de données vers les clusters voisins. Le Blackwell Ultra reste compatible avec l’écosystème CUDA tout en présentant des optimisations dédiées pour les frameworks IA de nouvelle génération. Les développeurs peuvent continuer à écrire du code CUDA programmatable, tout en profitant des moteurs d’accélération IA dédiés et du Transformer Engine de seconde génération. NVIDIA met également en avant l’existence d’un briefing technique qui cartographie les caractéristiques du silicium vers les résultats systèmes, offrant une vue détaillée de la chaîne silicium‑vers‑système. Plus de détails: https://developer.nvidia.com/blog/inside-nvidia-blackwell-ultra-the-chip-powering-the-ai-factory-era/. En résumé, Blackwell Ultra fournit une voie pragmatique et scalable pour les déploiements d’usines IA: compute robuste, mémoire abondante sur le package et interconnexions de haut débit qui réduisent la latence et augmentent le throughput par watt dans les scénarios IA industriels. L’orientation CUDA assure une transition facile des workflows existants vers cette plateforme tout en bénéficiant des accélérateurs IA et des innovations en mémoire et interconnexion. Pour les évaluateurs d’infrastructures IA, Blackwell Ultra représente un ensemble cohérent de capacités destinées à réduire le coût total de possession des déploiements à grande échelle, tout en rendant possibles des workloads IA plus ambitieux. Des informations et matériaux supplémentaires sur le silicium et l’écosystème sont disponibles via le post de NVIDIA mentionné ci‑dessus. Notes: le contenu ci‑dessous est une interprétation fidèle de la description officielle de NVIDIA concernant Blackwell Ultra, centrée sur l’intégration double die, l’accélération NVFP4, la mémoire massive et les innovations d’interconnexion pour les usines IA. Des éléments additionnels peuvent être consultés dans le NVIDIA Dev Blog indiqué.

More resources

CUDA Toolkit 13.0 pour Jetson Thor : Écosystème Arm Unifié et Plus

Kit CUDA unifié pour Arm sur Jetson Thor avec cohérence mémoire complète, partage du GPU entre processus, interop OpenRM/dmabuf, support NUMA et outils améliorés pour l’embarqué et le serveur.

Réduire les coûts de déploiement des modèles tout en conservant les performances grâce au swap de mémoire GPU

Exploitez le swap mémoire GPU (hot-swapping de modèles) pour partager les GPUs entre plusieurs LLM, réduire les coûts inoccupés et améliorer l’auto-Scaling tout en respectant les SLA.

Amélioration de l’auto-tuning GEMM avec nvMatmulHeuristics dans CUTLASS 4.2

Présente nvMatmulHeuristics pour sélectionner rapidement un petit ensemble de configurations de kernels GEMM à fort potentiel pour CUTLASS 4.2, réduisant considérablement le temps de tuning tout en approchant les performances d’une Recherche Exhaustive.

Accélérez ZeroGPU Spaces avec la compilation ahead-of-time (AoT) de PyTorch

Découvrez comment la compilation AoT de PyTorch accélère ZeroGPU Spaces en exportant un modèle compilé et en le rechargeant instantanément, avec quantification FP8, formes dynamiques et intégration au flux Spaces GPU.

Fine-Tuning gpt-oss pour la précision et les performances avec l’entraînement par quantisation (QAT)

Guide du fine-tuning de gpt-oss utilisant SFT + QAT pour récupérer la précision FP4 tout en préservant l’efficacité, avec upcast vers BF16, MXFP4, NVFP4 et déploiement avec TensorRT-LLM.

Comment les petits modèles linguistiques contribuent à une IA agentique évolutive

Explique comment les petits modèles linguistiques permettent une IA agentique plus rentable et flexible, aux côtés des LLMs, via NVIDIA NeMo et Nemotron Nano 2.