Construa Pipelines de Vision AI de Alto Desempenho com VC-6 Acelerado por CUDA da NVIDIA

Sources: https://developer.nvidia.com/blog/build-high-performance-vision-ai-pipelines-with-nvidia-cuda-accelerated-vc-6, https://developer.nvidia.com/blog/build-high-performance-vision-ai-pipelines-with-nvidia-cuda-accelerated-vc-6/, NVIDIA Dev Blog

TL;DR

- O rendimento de GPUs cresce mais rápido que os pipelines de dados tradicionais; isso pode levar a gargalos quando I/O, transferências PCIe e etapas CPU ficam para trás do desempenho do modelo. VC-6 é um codec projetado para execução massivamente paralela que se alinha naturalmente com GPUs.

- A versão CUDA acelerada do VC-6 (alpha) oferece hierarquia multi-resolução nativa, decodificação seletiva e recall de dados seletivo para reduzir I/O e largura de banda de memória, entregando tensores prontos para GPU.

- O caminho CUDA (vc6_cuda12) oferece uma biblioteca CUDA nativa e um wheel Python pré-compilado para instalação fácil; as saídas do decodificador podem expor o cuda_array_interface para uso com CuPy, PyTorch e nvImageCodec. Suporte a decodificação parcial e RoI permite buscar apenas os bytes necessários.

- Testes iniciais na DIV2K indicam economias de I/O entre ~37% e ~72% (conforme o objetivo de resolução), refletindo menor tráfego de rede, armazenamento, PCIe e memória VRAM em comparação com decodificação de resolução total. A arquitetura mapeia a hierarquia VC-6 ao modelo SIMT da GPU para maximizar o throughput.

- Mesmo na forma alfa, o caminho CUDA demonstra ganhos de desempenho em relação a OpenCL e CPU, abrindo caminho para mais otimizações de batching e melhorias de eficiência em toda a GPU. Para mais detalhes, consulte o post do NVIDIA Dev Blog sobre VC-6 acelerado por CUDA. NVIDIA Dev Blog

Contexto e antecedentes

À medida que o desempenho das GPUs aumenta, os pipelines de dados precisam acompanhar para não desperdiçar ciclos de computação. Codecs tradicionais costumam exigir a leitura de todo o arquivo para atender qualquer saída, impondo grandes movimentos de dados e processamento na CPU. O VC-6 (SMPTE ST 2117-1) foi desenvolvido para arquiteturas modernas de computação, gerando uma hierarquia multi-resolução eficiente em vez de um único bloco de pixels. Essa estrutura permite decodificação seletiva e fetch seletivo, com componentes como planos de cor, elencos ou blocos de imagem podendo ser acessados de forma independente e em paralelo. O resultado é um caminho de bits comprimidos para tensores prontos para a IA que se alinha melhor com a paralelização das GPUs. A hierarquia multi-resolução facilita reduções de resolução por potências de dois (8K → 4K → Full HD) e o processo de decodificação evolui mantendo a coerência entre camadas. A arquitetura enfatiza dependências mínimas para suportar processamento concorrente, o que a torna adequada para fluxos de trabalho de edição de vídeo de baixa latência em CPUs e OpenCL, além de atender às exigências de alto throughput de IA. O objetivo de criar uma implementação CUDA dedicada foi permitir otimizações específicas para IA e integração com o ecossistema de ferramentas como PyTorch. O VC-6 se destaca pela recuperação seletiva de dados: em vez de ler o fluxo inteiro, você obtém apenas os bytes necessários para um LoQ ou ROI específico. Isso reduz o tráfego de I/O e memória, resultando em pipelines de dados mais rápidos e com maior throughput para modelos de IA. Em testes com a DIV2K (800 imagens) em um RTX PRO 6000 Blackwell Server-Edition, a decodificação com CUDA mostrou ganhos de throughput em comparação aos caminhos CPU/OpenCL, especialmente em modos de throughput que se beneficiam de kernels maiores e menos overhead de chamadas.

Como a implementação CUDA se traduz em desempenho

A decodificação ocorre por meio de uma cadeia de kernels de upsampling que reconstrói a imagem por LoQs sucessivos. Em LoQs baixos, a computação útil é significativa, porém o overhead também pode ser relevante; a fusão de kernels e o uso de gráficos CUDA são estratégias esperadas para reduzir esse overhead. A observação de Nsight Systems aponta que decodificações únicas podem subutilizar a GPU quando cada kernel lança apenas um pequeno grid; consolidar o trabalho em grids maiores pode melhorar a eficiência do scheduler e permitir várias decodificações em paralelo. Para pipelines com várias decodificações, uma abordagem de threading no CPU com várias streams da GPU facilita a sobreposição de tarefas, mas lançar uma única grade maior no GPU costuma ser mais eficiente do que muitas decodificações independentes. Em termos práticos, o objetivo é reduzir a sobrecarga de CPU ao mesmo tempo em que se aproveita a capacidade de decodificar várias imagens em paralelo.

Detalhes técnicos ou Implementação

O VC-6 usa uma estrutura hierárquica multi-resolução com operações independentes em planos de cor, elencos ou tiles, o que facilita a paralelização em GPUs. A implementação CUDA explora essa estrutura para mapear tarefas de decodificação para threads e blocks, mantendo paralelismo sem dependências fortes entre operações. Recursos disponíveis com a versão CUDA incluem:

- Biblioteca CUDA nativa para throughput elevado em pipelines de IA.

- Pacote Python pré-compilado (vc6_cuda12) para instalação via pip e uso rápido com PyTorch, CuPy e bibliotecas relacionadas.

- Saídas de decodificador com interface cuda_array_interface para integração com bibliotecas GPU.

- Decodificação parcial e suporte a RoI para buscar apenas os dados necessários.

- Utilitários de inspeção de cabeçalho para estimar o tamanho necessário do LoQ alvo. Do ponto de vista do desenvolvedor, o caminho CUDA para VC-6 oferece um bloco de construção prático hoje, complementando bibliotecas existentes e atendendo a workloads de visão com alta taxa de transferência. Mestres da plataforma estão explorando como graphos CUDA e fusão de kernels podem reduzir overheads entre estágios de decodificação, aumentando o rendimento global do pipeline.

Principais conclusões

- VC-6 foi projetado para explorar o hardware moderno com uma arquitetura hierárquica multi-resolução que facilita decodificação seletiva e recall de dados.

- O caminho CUDA acelerado traz otimizações nativas, proporcionando ganhos de desempenho em relação a CPU e OpenCL, com integração prática ao ecossistema de IA.

- Decodificação parcial, RoI e recall seletivo reduzem significativamente o I/O e o tráfego de memória, ajudando a escalar throughput de loaders de dados sem alterar o código de modelo.

- Um wheel Python pronto para uso e suporte a cuda_array_interface tornam mais fácil experimentar com VC-6 em PyTorch, CuPy e afins.

- O trabalho em alfa aponta para maior batching nativo, redução de overhead de execução de kernels e evolução contínua para aproveitar melhor GPUs e gráficos CUDA.

Perguntas frequentes

-

O que é VC-6 e por que é relevante para pipelines de visão IA?

VC-6 é um codec de codificação de imagem/vídeo conforme SMPTE ST 2117-1, projetado para interação eficiente com arquiteturas modernas de computação, com foco em decodificação multi-resolução hierárquica e recall seletivo de dados para workloads de IA. A versão CUDA acelera essa arquitetura para GPUs, reduzindo movimentos de dados e aumentando o throughput.

-

Como instalar e começar a usar VC-6 com CUDA?

O pacote CUDA vc6_cuda12 é distribuído como um wheel Python pré-compilado, facilitando a instalação via pip e a criação de objetos de codec para encoding, decoding e transcoding. O decodificador pode expor interface de array CUDA para uso com PyTorch, CuPy e bibliotecas afins.

-

É possível decodificar apenas parte de um arquivo ou imagem? Como funciona o RoI?

Sim. Decodificação parcial e suporte a RoI permitem ler e processar apenas os dados necessários para um LoQ ou região específica, reduzindo I/O e uso de memória. Um utilitário permite estimar o tamanho necessário para o LoQ alvo.

-

uais são as limitações atuais e direções futuras do caminho CUDA?

O caminho CUDA está em alpha, com batching nativo e mais otimizações no roadmap. O trabalho continua para melhorar o throughput, reduzir overhead de launch de kernels e expandir o processamento direto na GPU.

Referências

- NVIDIA Dev Blog: Build High-Performance Vision AI Pipelines with NVIDIA CUDA-Accelerated VC-6. https://developer.nvidia.com/blog/build-high-performance-vision-ai-pipelines-with-nvidia-cuda-accelerated-vc-6/

More news

NVIDIA HGX B200 reduz a Intensidade de Emissões de Carbono Incorporado

O HGX B200 da NVIDIA reduz 24% da intensidade de carbono incorporado em relação ao HGX H100, ao mesmo tempo em que aumenta o desempenho de IA e a eficiência energética. Esta análise resume os dados de PCF e as novidades de hardware.

Prever Eventos Climáticos Extremos em Minutos sem Supercomputador com Huge Ensembles (HENS)

NVIDIA e o Lawrence Berkeley National Laboratory apresentam Huge Ensembles (HENS), uma ferramenta de IA de código aberto que prevê eventos climáticos raros e de alto impacto usando 27.000 anos de dados, com opções de código aberto ou prontos para uso.

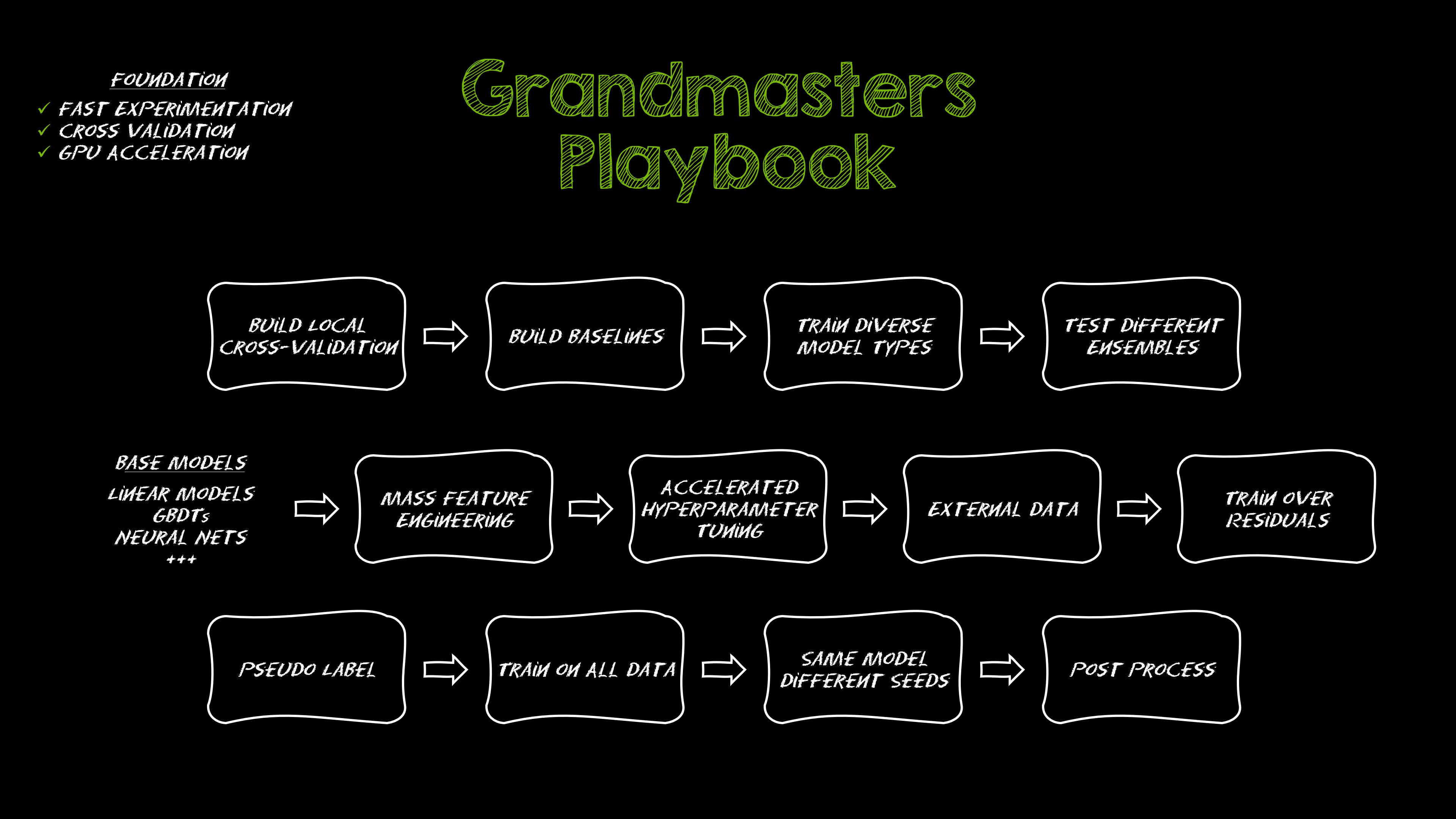

Playbook dos Grandmasters do Kaggle: 7 Técnicas de Modelagem Testadas para Dados Tabulares

Análise detalhada de sete técnicas testadas por Grandmasters do Kaggle para resolver grandes conjuntos de dados tabulares com aceleração por GPU, desde baselines diversificados até ensemble avançado e pseudo-rotulagem.

Como reduzir gargalos do KV Cache com NVIDIA Dynamo

O Dynamo da NVIDIA transfere o KV Cache da memória da GPU para armazenamento de custo mais baixo, permitindo janelas de contexto maiores, maior concorrência e menor custo de inferência em grandes modelos.

Microsoft transforma site da Foxconn no data center Fairwater AI, considerado o mais poderoso do mundo

A Microsoft divulga planos para um data center Fairwater AI de 1,2 milhão de pés quadrados no Wisconsin, com centenas de milhares de GPUs Nvidia GB200. projeto de US$ 3,3 bilhões promete treinamento de IA em escala sem precedentes.

NVIDIA RAPIDS 25.08 Adiciona Novo Profiler para cuML, Melhorias no Motor GPU Polars e Suporte Ampliado de Algoritmos

RAPIDS 25.08 traz profiladores function-level e line-level para cuml.accel, executor streaming padrão no motor GPU Polars, suporte ampliado de tipos e strings, novo Spectral Embedding no cuML e acelerações com zero código para mais algoritmos.