Concevoir des pipelines Vision AI haute performance avec VC-6 accéléré par CUDA de NVIDIA

Sources: https://developer.nvidia.com/blog/build-high-performance-vision-ai-pipelines-with-nvidia-cuda-accelerated-vc-6, https://developer.nvidia.com/blog/build-high-performance-vision-ai-pipelines-with-nvidia-cuda-accelerated-vc-6/, NVIDIA Dev Blog

TL;DR

- Le débit des GPUs augmente plus vite que les pipelines de données traditionnels; les goulots d’étranglement surviennent lorsque l’E/S, les transferts PCIe et les étapes CPU ne suivent pas le rythme des modèles. VC-6 est un codec conçu pour une exécution massivement parallèle et s’adapte naturellement aux GPUs.

- VC-6 accéléré par CUDA (alpha) fournit une hiérarchie multi-résolution native, un décodage sélectif et un recall sélectif des données pour réduire les E/S et la largeur de bande mémoire, tout en livrant des tenseurs prêts pour le GPU.

- Le chemin CUDA (vc6_cuda12) propose une bibliothèque CUDA native et une wheel Python pré-compilée pour une installation facile; le décodeur peut exposer cuda_array_interface afin d’être utilisé avec CuPy, PyTorch et nvImageCodec. Le décodage partiel et le RoI permettent de ne récupérer que les octets nécessaires.

- Des tests préliminaires sur l’ensemble de données DIV2K montrent des économies d’E/S d’environ 37% à 72% selon la résolution cible, reflétant une réduction du trafic réseau, stockage, PCIe et VRAM par rapport au décodage en résolution complète. L’architecture associe la hiérarchie VC-6 au modèle SIMT des GPUs pour maximiser le débit.

- Même à l’état alpha, le chemin CUDA démontre des gains significatifs face à OpenCL et CPU, en ouvrant la voie à des optimisations de batching et à des améliorations d’efficacité sur le GPU. Pour plus de détails, consultez le post du NVIDIA Dev Blog sur VC-6 accéléré par CUDA. NVIDIA Dev Blog

Contexte et arrière-plan

À mesure que les performances des GPUs augmentent, les pipelines de données doivent suivre pour ne pas laisser le processeur graphique attendre. Les codecs traditionnels présentent souvent l’image comme un bloc plat et nécessitent la lecture de tout le fichier pour produire une sortie quelconque, entraînant des déplacements importants de données et du travail côté CPU. VC-6 (SMPTE ST 2117-1) est conçu dès le départ pour les architectures modernes de calcul, générant une hiérarchie multi-résolution efficace plutôt qu’un seul bloc d’images. Cette structure autorise le décodage sélectif et le fetch sélectif, avec des composants (plans de couleur, échelons, tuiles image) accessibles indépendamment et en parallèle. Cela donne une voie des bits compressés vers des tenseurs prêts pour l’IA mieux adaptée au parallélisme des GPUs. La hiérarchie multi-résolution permet des diminutions de résolution par des puissances de deux (8K → 4K → Full HD) et le processus de décodage se reconstruit en progressant par upsampling et ajout des résiduels. L’architecture vise à minimiser les dépendances, afin de soutenir un traitement concurrent et un débit élevé, ce qui en fait un choix naturel pour les flux de travail IA exigeants. L’objectif était d’adapter VC-6 à CUDA afin d’optimiser les flux de données vers les pipelines IA et de s’intégrer sans friction dans les outils IA existants. L’atout principal de VC-6 réside dans le recall sélectif des données: au lieu de lire tout le flux, on lit uniquement les octets nécessaires pour un LoQ ou une ROI donnée. Cela se traduit par une réduction des E/S et de l’utilisation mémoire, et par conséquent par une augmentation du débit global des pipelines de données vers les réseaux de neurones.

Comment la mise en œuvre CUDA se traduit par des performances

La décodification suit une chaîne de kernels d’upsampling reconstruisant l’image sur des LoQ successifs. À bas LoQ, la proportion de calcul utile est élevée, mais la surcharge peut aussi être significative; l’optimisation CUDA inclut la fusion de kernels et l’utilisation de graphes CUDA pour réduire les frais généraux entre les étapes. Les traces Nsight Systems montrent que les premières décodages peuvent sous-utiliser le GPU lorsque chaque kernel lance un seul bloc; regrouper les charges dans des grilles plus grandes améliore l’efficacité du scheduler et permet de lancer plusieurs décodages en parallèle sans conflits. Dans les pipelines avec plusieurs décodeurs, il est plus efficace de lancer une seule grille plus grande plutôt que plusieurs décodeurs individuels qui s’exécutent en parallèle sur le CPU et des streams distincts. Cette approche réduit aussi fortement la surcharge CPU et maximise l’utilisation du GPU pour les tâches de décodage résiduel et de reconstruction.

Détails techniques ou Mise en œuvre

VC-6 repose sur une architecture hiérarchique multi-résolution qui permet des accès indépendants et parallèles à des éléments comme plans de couleur, échelons ou tuiles d’image, facilitant la parallélisation sur les GPUs. La mise en œuvre CUDA exploite cette structure pour mapper les tâches de décodage sur des threads et des blocs tout en conservant le parallélisme et en minimisant les dépendances. Les fonctionnalités CUDA incluent:

- Une bibliothèque CUDA native visant un débit élevé dans les pipelines IA.

- Un package Python prêt à l’emploi (vc6_cuda12) pour installation via pip et utilisation avec PyTorch, CuPy et autres bibliothèques.

- Des sorties de décodeur pouvant exposer l’interface de tableau CUDA (cuda_array_interface) pour une intégration transparente avec les bibliothèques GPU.

- Décodage partiel et support RoI permettant de récupérer uniquement les données nécessaires.

- Des outils pour pré-visualiser l’en-tête et estimer la taille nécessaire du LoQ cible. Du point de vue développeur, le chemin CUDA pour VC-6 offre un bloc de construction pratique aujourd’hui et se veut complémentaire des bibliothèques existantes, répondant aux workloads IA à haut débit qui exigent une récupération ciblée des données et du rendu sur le GPU.

Points clés à retenir

- VC-6 est conçu pour exploiter les architectures GPU modernes via une architecture hiérarchique multi-résolution favorisant le décodage sélectif et le recall des données.

- Le chemin CUDA apporte des optimisations natives et des gains de performance significatifs par rapport au CPU et à OpenCL, tout en facilitant l’intégration avec les outils IA populaires.

- Le décodage partiel et le RoI réduisent fortement les E/S et le trafic mémoire, aidant à faire évoluer le throughput des loaders sans modifier le code des modèles.

- Un wheel Python prêt à l’emploi et le support de cuda_array_interface simplifient l’expérimentation avec VC-6 dans PyTorch, CuPy et l’écosystème GPU.

- Le travail en alpha ouvre la voie à des améliorations de batching et à une réduction continue des overheads liés à l’exécution des kernels.

FAQ

Références

- NVIDIA Dev Blog: Build High-Performance Vision AI Pipelines with NVIDIA CUDA-Accelerated VC-6. https://developer.nvidia.com/blog/build-high-performance-vision-ai-pipelines-with-nvidia-cuda-accelerated-vc-6/

More news

NVIDIA HGX B200 réduit l’intensité des émissions de carbone incorporé

Le HGX B200 de NVIDIA abaisse l’intensité des émissions de carbone incorporé de 24% par rapport au HGX H100, tout en offrant de meilleures performances IA et une efficacité énergétique accrue. Cet article résume les données PCF et les nouveautés matérielles.

Prévoir les phénomènes météorologiques extrêmes en quelques minutes sans superordinateur : Huge Ensembles (HENS)

NVIDIA et le Lawrence Berkeley National Laboratory présentent Huge Ensembles (HENS), un outil IA open source qui prévoit des événements météorologiques rares et à fort impact sur 27 000 années de données, avec des options open source ou prêtes à l’emploi.

Comment réduire les goulots d’étranglement KV Cache avec NVIDIA Dynamo

NVIDIA Dynamo déporte le KV Cache depuis la mémoire GPU vers un stockage économique, permettant des contextes plus longs, une meilleure concurrence et des coûts d’inférence réduits pour les grands modèles et les charges AI génératives.

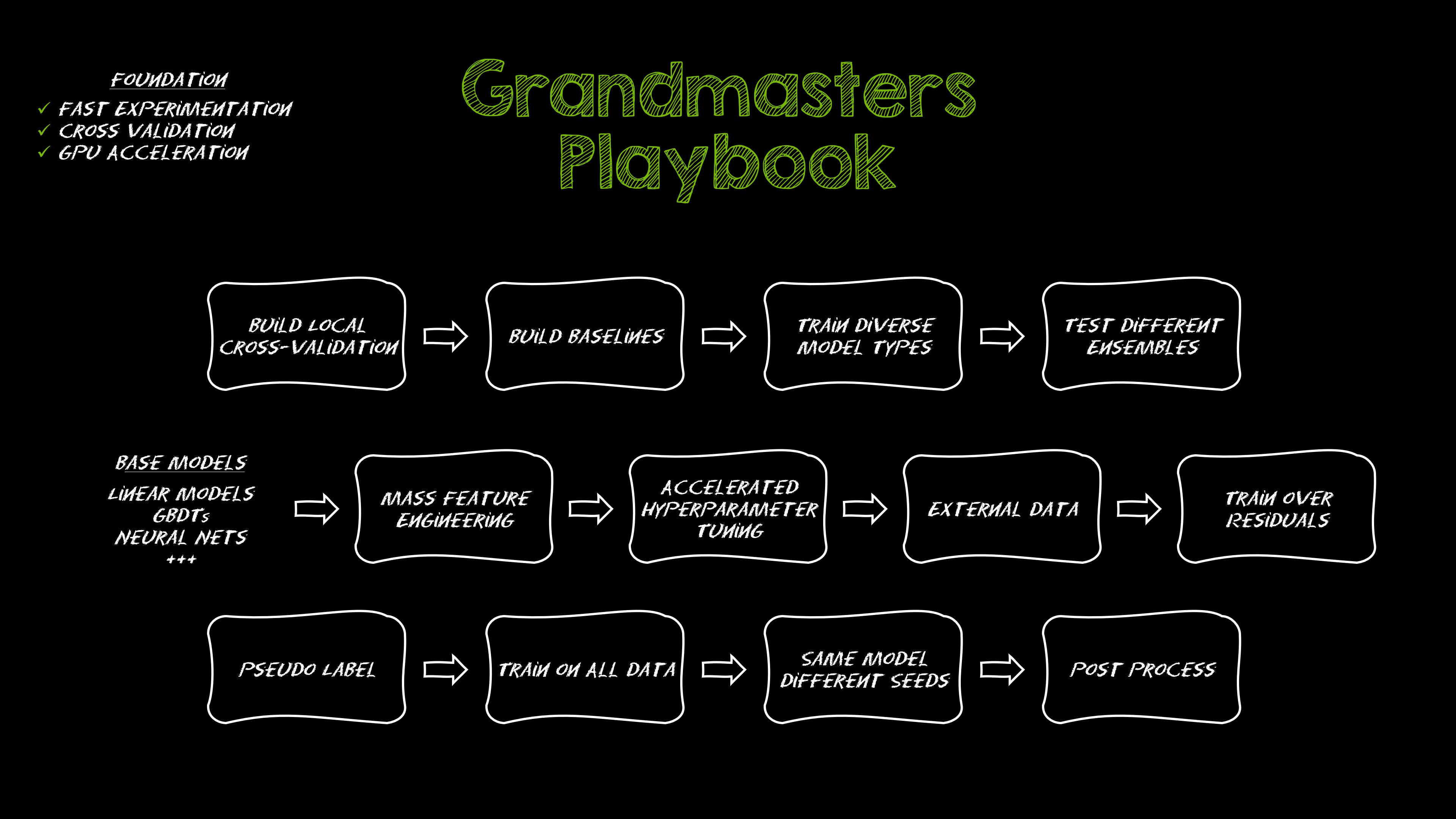

Le Playbook des Grands Maîtres Kaggle: 7 Techniques de Modélisation pour Données Tabulaires

Analyse approfondie de sept techniques éprouvées par les Grands Maîtres Kaggle pour résoudre rapidement des ensembles de données tabulaires à l’aide d’une accélération GPU, des baselines divers à l’assemblage et à la pseudo-étiquetage.

Microsoft transforme le site Foxconn en data center Fairwater AI, présenté comme le plus puissant au monde

Microsoft dévoile des plans pour un data center Fairwater AI de 1,2 million de mètres carrés au Wisconsin, abritant des centaines de milliers de GPU Nvidia GB200. Le projet de 3,3 milliards de dollars promet un entraînement IA sans précédent.

NVIDIA RAPIDS 25.08 Ajoute un Nouveau Profiler pour cuML, Améliorations du moteur GPU Polars et Support d’Algorithmes Étendu

RAPIDS 25.08 introduit deux profils pour cuml.accel (fonctionnel et ligne), l’exécuteur streaming par défaut du moteur Polars GPU, un support de types et chaînes étendu, Spectral Embedding dans cuML et des accélérations zéro-code pour plusieurs estimateurs.