Construir flujos Vision AI de alto rendimiento con VC-6 Acelerado por CUDA de NVIDIA

Sources: https://developer.nvidia.com/blog/build-high-performance-vision-ai-pipelines-with-nvidia-cuda-accelerated-vc-6, https://developer.nvidia.com/blog/build-high-performance-vision-ai-pipelines-with-nvidia-cuda-accelerated-vc-6/, NVIDIA Dev Blog

TL;DR

- El rendimiento de la GPU crece más rápido que los pipelines de datos tradicionales; los cuellos de botella aparecen cuando I/O, PCIe y procesamiento en CPU no siguen el ritmo de los modelos. VC-6 es un códec diseñado para ejecución masivamente paralela que se alinea naturalmente con las GPUs.

- VC-6 acelerado por CUDA (alpha) ofrece jerarquía multi‑resolución nativa, decodificación selectiva y recall de datos selectivo para reducir I/O y ancho de banda de memoria, entregando tensores listos para la GPU.

- El camino CUDA (vc6_cuda12) incluye una biblioteca CUDA nativa y una rueda de Python precompilada para instalación fácil; las salidas del decodificador pueden exponer cuda_array_interface para usar con CuPy, PyTorch y nvImageCodec. El soporte para decodificación parcial y RoI permite obtener solo los bytes necesarios.

- Pruebas iniciales en DIV2K muestran ahorros de I/O de aproximadamente 37% a 72% según la resolución objetivo, reflejando menor tráfico de red, almacenamiento, PCIe y VRAM frente a la decodificación de resolución total. La arquitectura une la jerarquía VC-6 con el modelo SIMT de las GPUs para maximizar el rendimiento.

- Aunque está en etapa alfa, el camino CUDA demuestra ganancias significativas frente a OpenCL y CPU, sentando las bases para mejoras de batching y optimización de uso de GPU. Para más detalles, consulta el post del NVIDIA Dev Blog sobre VC-6 acelerado por CUDA. NVIDIA Dev Blog

Contexto y antecedentes

A medida que las GPUs aumentan su rendimiento, los pipelines de datos deben mantenerse al día para no hacer esperar al acelerador. Los códecs tradicionales suelen presentar la imagen como un bloque plano y requieren leer todo el archivo para generar cualquier salida, lo que implica grandes movimientos de datos y procesamiento en CPU. VC-6 (SMPTE ST 2117-1) está diseñado desde cero para las arquitecturas informáticas modernas, generando una jerarquía multi‑resolución eficiente en lugar de un único bloque de píxeles. Esta estructura permite decodificación selectiva y fetch selectivo, con componentes como planos de color, estratos o teselas de imagen accesibles de forma independiente y en paralelo. El resultado es un camino de bits comprimidos a tensores listos para IA mejor alineados con el paralelismo de las GPUs. La jerarquía multi‑resolución facilita reducciones de resolución por potencias de dos (8K → 4K → Full HD) y el proceso de decodificación se reconstruye progresivamente mediante upsampling y la suma de residuales. La arquitectura busca minimizar dependencias para apoyar procesamiento concurrente y alto throughput, lo que la hace adecuada para flujos de trabajo de edición de vídeo de baja latencia en CPU y OpenCL, y para demandas de IA de alto rendimiento. El objetivo fue adaptar VC-6 a CUDA para optimizar flujos de datos hacia IA y facilitar la integración con herramientas IA comunes. La ventaja principal de VC-6 es el recall selectivo de datos: en lugar de leer todo el flujo, se obtienen únicamente los bytes necesarios para un LoQ o ROI concreto. Esto reduce I/O y uso de memoria, resultando en mayores throughput para los pipelines de datos hacia modelos de IA.

Cómo la implementación CUDA se traduce en rendimiento

La decodificación sigue una cadena de kernels de upsampling que reconstruyen la imagen en LoQ sucesivos. En LoQ bajos, la parte útil del cómputo es significativa, pero la sobrecarga también puede ser relevante; se esperan optimizaciones como gráficos CUDA y fusión de kernels para reducir la sobrecarga entre etapas. Las trazas de Nsight Systems muestran que los primeros decodificadores pueden subutilizar la GPU cuando cada kernel lanza un único bloque; consolidar el trabajo en grids más grandes mejora la eficiencia del planificador y permite ejecutar varias decodificaciones en paralelo sin conflictos. En pipelines con varios decodificadores, es más eficiente lanzar una única grilla grande en la GPU que múltiples decodificadores paralelos desde la CPU. Esto reduce también la sobrecarga de CPU y maximiza la utilización de la GPU para las etapas residuales y de reconstrucción.

Detalles técnicos o Implementación

VC-6 se apoya en una arquitectura jerárquica multi‑resolución que permite accesos independientes y paralelos a componentes como planes de color, estratos o teselas de imagen, facilitando la paralelización en GPUs. La implementación CUDA aprovecha esta estructura para mapear tareas de decodificación a hilos y bloques con mínimo acceso secuencial entre etapas. Las características CUDA disponibles incluyen:

- Una biblioteca CUDA nativa para alto throughput en pipelines IA.

- Un paquete Python listo para usar (vc6_cuda12) para instalación vía pip y uso con PyTorch, CuPy y bibliotecas afines.

- Salidas de decodificador con interfaz de array CUDA para integración con bibliotecas GPU.

- Decodificación parcial y soporte RoI para obtener solo los datos necesarios.

- Utilidad para inspeccionar cabeceras e estimar el tamaño necesario del LoQ objetivo. Desde la perspectiva del desarrollador, la ruta CUDA para VC-6 ofrece un bloque de construcción práctico hoy y se propone como complemento de bibliotecas existentes, cubriendo workloads IA con alta demanda de throughput y recuperación selectiva de datos para GPU.

Conclusiones clave

- VC-6 está diseñado para explotar GPUs modernas mediante una arquitectura jerárquica multi‑resolución que facilita decodificación selectiva y recall de datos.

- La ruta CUDA aporta optimizaciones nativas y mejoras de rendimiento frente a CPU y OpenCL, con integración directa en herramientas IA populares.

- La decodificación parcial y RoI reducen notablemente I/O y uso de memoria, ayudando a escalar throughput sin cambiar el código del modelo.

- Un wheel Python preempaquetado y el soporte de cuda_array_interface facilitan probar VC-6 en PyTorch, CuPy y ecosistemas GPU.

- El desarrollo en alfa abre la puerta a mejoras de batching y a una reducción continua de los overheads de ejecución de kernels.

Preguntas frecuentes

-

¿Qué es VC-6 y por qué es relevante para pipelines Vision IA?

VC-6 es un codec de codificación de imágenes/vídeos conforme a SMPTE ST 2117-1, diseñado para interactuar eficientemente con arquitecturas de cómputo modernas, con una jerarquía multi‑resolución y recall selectivo de datos para workloads IA. La implementación CUDA traduce esto para GPUs, reduciendo movimientos de datos y aumentando el throughput.

-

¿Cómo instalar y empezar a usar VC-6 con CUDA?

El paquete CUDA vc6_cuda12 se distribuye como wheel Python pre‑compilada, instalable vía pip. Permite crear objetos de codec para codificar, decodificar y transcodificar, y el decodificador puede exponer la interfaz de array CUDA para PyTorch, CuPy y nvImageCodec.

-

¿Es posible decodificar solo parte de un archivo o imagen? ¿Cómo funciona RoI?

Sí. La decodificación parcial y el RoI permiten leer y procesar solo los datos requeridos para un LoQ o ROI específico, reduciendo I/O y uso de memoria. Se provee una utilidad para estimar el tamaño necesario del LoQ objetivo.

-

¿Cuáles son las limitaciones actuales y direcciones futuras del camino CUDA?

El camino CUDA está en alfa, con batching nativo y mejoras planificadas. Se busca mejorar throughput, reducir overhead de lanzamiento de kernels y expandir el procesamiento en GPU.

Referencias

- NVIDIA Dev Blog: Build High-Performance Vision AI Pipelines with NVIDIA CUDA-Accelerated VC-6. https://developer.nvidia.com/blog/build-high-performance-vision-ai-pipelines-with-nvidia-cuda-accelerated-vc-6/

More news

NVIDIA HGX B200 reduce la intensidad de las emisiones de carbono incorporado

El HGX B200 de NVIDIA reduce la intensidad de carbono incorporado en un 24% frente al HGX H100, al tiempo que ofrece mayor rendimiento de IA y eficiencia energética. Este artículo resume los datos PCF y las novedades de hardware.

Predecir Eventos Climáticos Extremos en Minutos sin Supercomputadora: Huge Ensembles (HENS)

NVIDIA y Berkeley Lab presentan Huge Ensembles (HENS), una herramienta de IA de código abierto que pronostica eventos climáticos raros y de alto impacto usando 27,000 años de datos, con opciones de código abierto o listas para usar.

Cómo reducir cuellos de botella KV Cache con NVIDIA Dynamo

NVIDIA Dynamo offloads KV Cache desde la memoria de la GPU hacia almacenamiento económico, habilitando contextos más largos, mayor concurrencia y costos de inferencia más bajos para grandes modelos y cargas de IA generativa.

Microsoft transforma el sitio de Foxconn en el data center Fairwater AI, descrito como el más poderoso del mundo

Microsoft anuncia planes para un data center Fairwater AI de 1,2 millones de pies cuadrados en Wisconsin, con cientos de miles de GPU Nvidia GB200. El proyecto de 3.3 mil millones de dólares promete un entrenamiento de IA sin precedentes.

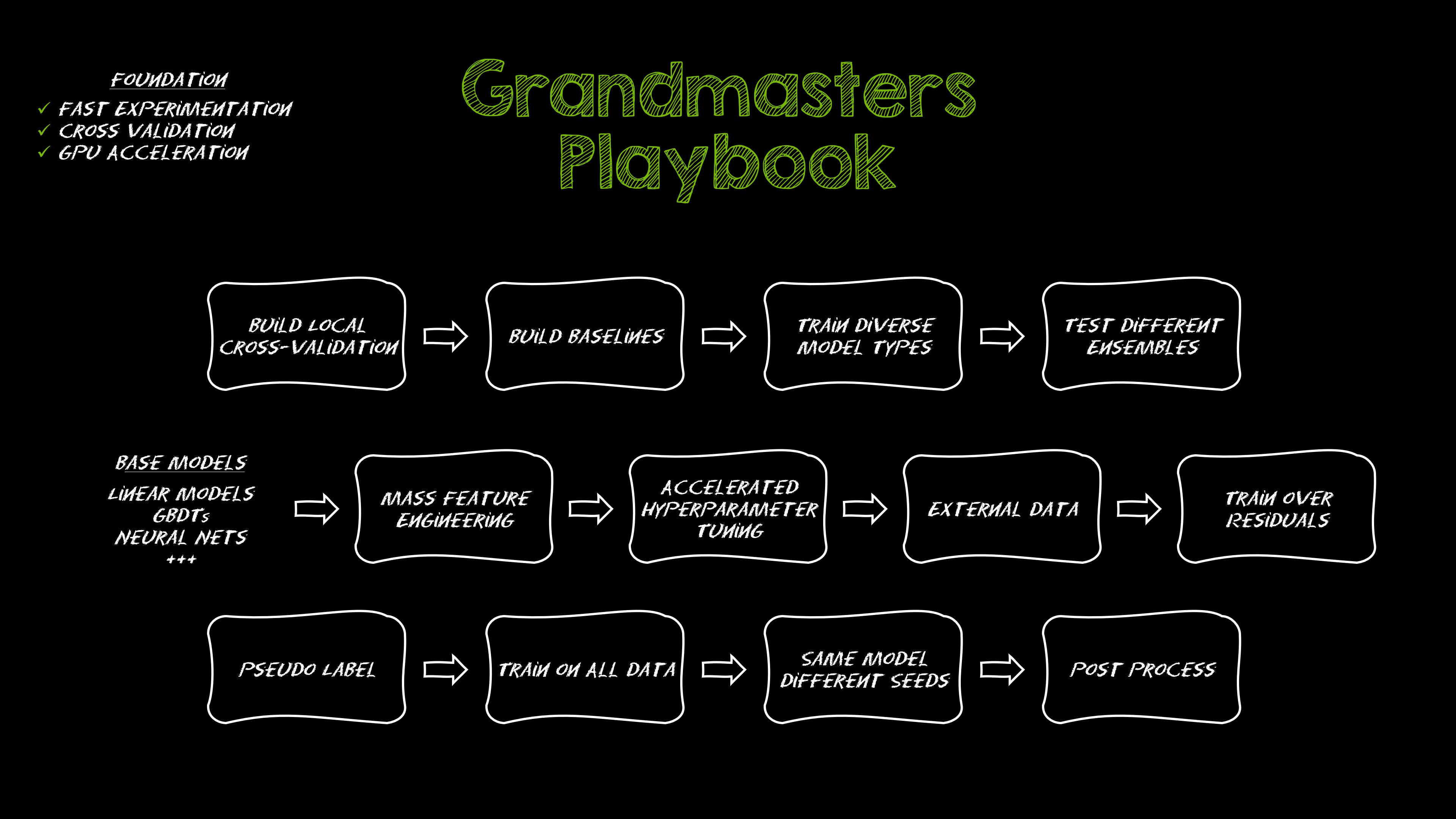

Manual de los Grandmasters de Kaggle: 7 Técnicas de Modelado para Datos Tabulares

Un análisis detallado de siete técnicas probadas por los Grandmasters de Kaggle para resolver rápidamente conjuntos de datos tabulares mediante aceleración por GPU, desde baselines variados hasta ensamblaje y pseudo-etiquetado.

NVIDIA RAPIDS 25.08 Agrega Nuevo profiler para cuML, Mejoras en el motor GPU de Polars y Soporte Ampliado de Algoritmos

RAPIDS 25.08 introduce perfiles de nivel de función y de línea para cuml.accel, el ejecutor de streaming por defecto del motor Polars GPU, soporte ampliado de tipos y cadenas, Spectral Embedding en cuML y aceleraciones de cero código para varios estimadores.