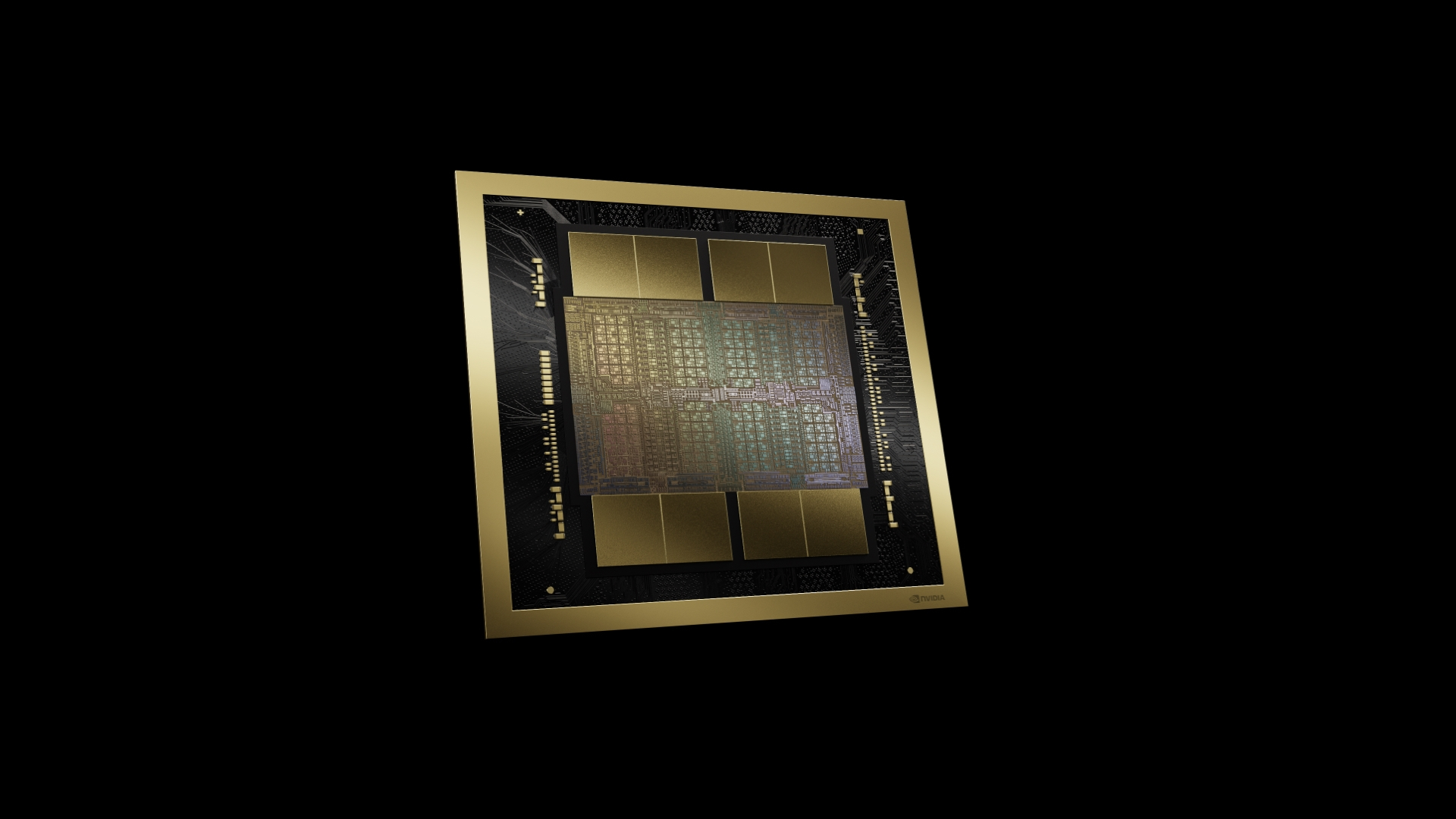

Dentro de NVIDIA Blackwell Ultra: el chip que impulsa la era de la fábrica de IA

Sources: https://developer.nvidia.com/blog/inside-nvidia-blackwell-ultra-the-chip-powering-the-ai-factory-era, https://developer.nvidia.com/blog/inside-nvidia-blackwell-ultra-the-chip-powering-the-ai-factory-era/, NVIDIA Dev Blog

TL;DR

- NVIDIA Blackwell Ultra es el último miembro de la arquitectura Blackwell, diseñado para acelerar el entrenamiento y el razonamiento de IA en servicios en tiempo real a gran escala.

- Utiliza un diseño de doble-die conectado por NV-HBI, con 10 TB/s de ancho de banda y un acelerador CUDA programable con 208 mil millones de transistores en un proceso TSMC 4NP.

- El GPU tiene 160 SM distribuidos en ocho GPC, con cuatro Tensor Cores por SM (640 en total), optimizados para NVFP4 y 256 KB de TMEM por SM.

- Blackwell Ultra ofrece hasta 15 petaFLOPS de NVFP4, 288 GB de HBM3e por GPU, memoria unificada de 1 TB y procesamiento de atención mejorado para modelos contextuales muy grandes.

- Para implementaciones en centros de datos, Blackwell Ultra admite NVLink (GPU–GPU), NVLink-C2C (interoperabilidad con Grace CPU) y PCIe Gen 6 x16, con conectividad de red ConnectX-8 para fábricas de IA a gran escala.

Contexto e historia

La era de la fábrica de IA exige hardware que escale tanto en cómputo como en memoria con alta eficiencia. Blackwell Ultra se presenta como la culminación de innovaciones en silicio e integración a nivel de sistema para acelerar el entrenamiento y el razonamiento IA en servicios en tiempo real y a gran escala. El diseño emplea dos dies retículo-tamaño conectados por NV-HBI para proporcionar un camino de datos de alta velocidad (10 TB/s) entre los dies, manteniéndose como un acelerador CUDA-programable para los desarrolladores. Blackwell Ultra está fabricado por TSMC 4NP y contiene 208 mil millones de transistores—aproximadamente 2,6x más que el Hopper. El corazón del dispositivo se compone de 160 SMs organizados en ocho GPC. Cada SM ofrece la capacidad de cómputo necesaria para cargas de trabajo modernas de IA, incluida la aceleración de operaciones de atención que dominan los modelos basados en transformadores.

Novedades

Blackwell Ultra introduce avances arquitectónicos y de capacidad para aumentar el throughput, reducir la latencia y ampliar la memoria para los modelos IA más grandes:

- Cores Tensor de quinta generación en todos los SM, con un segundo Transformer Engine para mayor throughput y menor latencia en workloads densos y dispersos de IA.

- Cuatro Tensor Cores por SM (640 en total), actualizados para NVFP4.

- 256 KB de TMEM por SM para mantener los datos cerca de las unidades de cómputo y soportar MMA de doble bloque de hilos.

- Precisión NVFP4: formato de 4 bits con escalado FP8/FP32 para cuantización por hardware con alta precisión y menor footprint de memoria.

- Rendimiento NVFP4 de hasta 15 petaFLOPS (Ultra) frente a 10 petaFLOPS en Blackwell, aportando mejoras en workloads densos e inferencia a gran escala.

- Aceleración de atención: el rendimiento SFU para instrucciones clave de atención se duplica, mitigando cuellos de botella en modelos con ventanas contextuales largas.

- Memoria: 288 GB de HBM3e por GPU, 3,6x más memoria on‑chip que H100 y 50% más que Blackwell, permitiendo modelos con parámetros realmente grandes y ventanas de contexto extensas.

- Conectividad: NVLink para comunicación GPU-GPU, NVLink-C2C para coherencia con Grace CPU y PCIe Gen 6 x16 para hosts; redes ConnectX-8 ofrecen alto rendimiento.

- Implementación en sistema: Grace CPU + dos GPUs Blackwell Ultra, con hasta 30 PFLOPS densos y 40 PFLOPS dispersos en NVFP4, con 1 TB de memoria unificada y red de 800 GB/s ConnectX-8.

Por qué importa (impacto para desarrolladores/empresas)

Blackwell Ultra representa un salto en eficiencia operativa y throughput IA para fábricas de IA de producción. La combinación de mayor densidad de memoria, precisión eficiente y doble throughput de atención se traduce en más instancias de modelo, respuestas más rápidas y menores costos por token generado en inferencia a gran escala. La memoria de 288 GB por GPU facilita alojar modelos de trillones de parámetros y ventanas de contexto extensas sin depender tanto del KV-cache. Para empresas que implementan servicios de IA, la arquitectura impacta dos métricas clave:

- Tokens por segundo por usuario (TPS/usuario): la aceleración del softmax y del procesamiento de atención reduce la latencia de inferencia en tiempo real.

- Tokens por segundo por megavatio (TPS/MW): más memoria y movimientos de datos más eficientes mejoran la eficiencia del data center, permitiendo más trabajo por vatio.

Detalles técnicos o implementación

El diseño Blackwell Ultra se centra en la integración de dos dies mediante NV-HBI, proporcionando 10 TB/s de ancho de banda entre ellos. El chip contiene 208 mil millones de transistores en un proceso TSMC 4NP, permitiendo una arquitectura de cómputo densa que mantiene la compatibilidad con CUDA. Elementos clave:

- 160 SMs organizados en ocho GPCs.

- Cada SM tiene cuatro Tensor Cores (640 en total) con NVFP4.

- 256 KB de TMEM por SM para mantener datos cerca de las unidades de cálculo.

- MMA de doble bloque de hilos: SMs emparejados cooperan en una operación MMA para reducir el tráfico de memoria.

- NVFP4: formato de 4 bits con escalado FP8/FP32 para cuantización eficiente con precisión cercana a FP8.

- Rendimiento NVFP4 de hasta 15 petaFLOPS (Ultra) frente a 10 petaFLOPS en Blackwell.

- Aceleración de atención: SFU con doble rendimiento para instrucciones de atención.

- Memoria de 288 GB HBM3e por GPU y memoria unificada de hasta 1 TB en configuraciones adecuadas.

- Interconexiones: NVLink para GPU-GPU, NVLink-C2C para coherencia con Grace, PCIe Gen 6 x16 para hosts; red ConnectX-8 a 800 GB/s.

- Despliegue en rack: Grace CPU + dos GPUs Ultra, con 30 PFLOPS densos y 40 PFLOPS dispersos, 1 TB de memoria unificada y red de alto rendimiento.

Conclusiones clave

- Blackwell Ultra combina integración de doble-die, NV-HBI y una memoria densa para IA en fábrica.

- NVFP4 permite cuantización eficiente con altas tasas de precisión en inferencia de IA.

- Aceleración de atención y mayor memoria permiten modelos más grandes y ventanas contextuales más largas sin depender excesivamente del KV-cache.

- El diseño mejora la eficiencia energética y el throughput, con conectividad robusta para implementaciones completas desde host hasta GPU.

- Las opciones NVLink, NVLink-C2C y PCIe Gen 6 soportan despliegues escalables desde una GPU hasta centros de datos de fábrica.

Preguntas frecuentes

Referencias

More news

NVIDIA HGX B200 reduce la intensidad de las emisiones de carbono incorporado

El HGX B200 de NVIDIA reduce la intensidad de carbono incorporado en un 24% frente al HGX H100, al tiempo que ofrece mayor rendimiento de IA y eficiencia energética. Este artículo resume los datos PCF y las novedades de hardware.

Predecir Eventos Climáticos Extremos en Minutos sin Supercomputadora: Huge Ensembles (HENS)

NVIDIA y Berkeley Lab presentan Huge Ensembles (HENS), una herramienta de IA de código abierto que pronostica eventos climáticos raros y de alto impacto usando 27,000 años de datos, con opciones de código abierto o listas para usar.

Cómo reducir cuellos de botella KV Cache con NVIDIA Dynamo

NVIDIA Dynamo offloads KV Cache desde la memoria de la GPU hacia almacenamiento económico, habilitando contextos más largos, mayor concurrencia y costos de inferencia más bajos para grandes modelos y cargas de IA generativa.

Microsoft transforma el sitio de Foxconn en el data center Fairwater AI, descrito como el más poderoso del mundo

Microsoft anuncia planes para un data center Fairwater AI de 1,2 millones de pies cuadrados en Wisconsin, con cientos de miles de GPU Nvidia GB200. El proyecto de 3.3 mil millones de dólares promete un entrenamiento de IA sin precedentes.

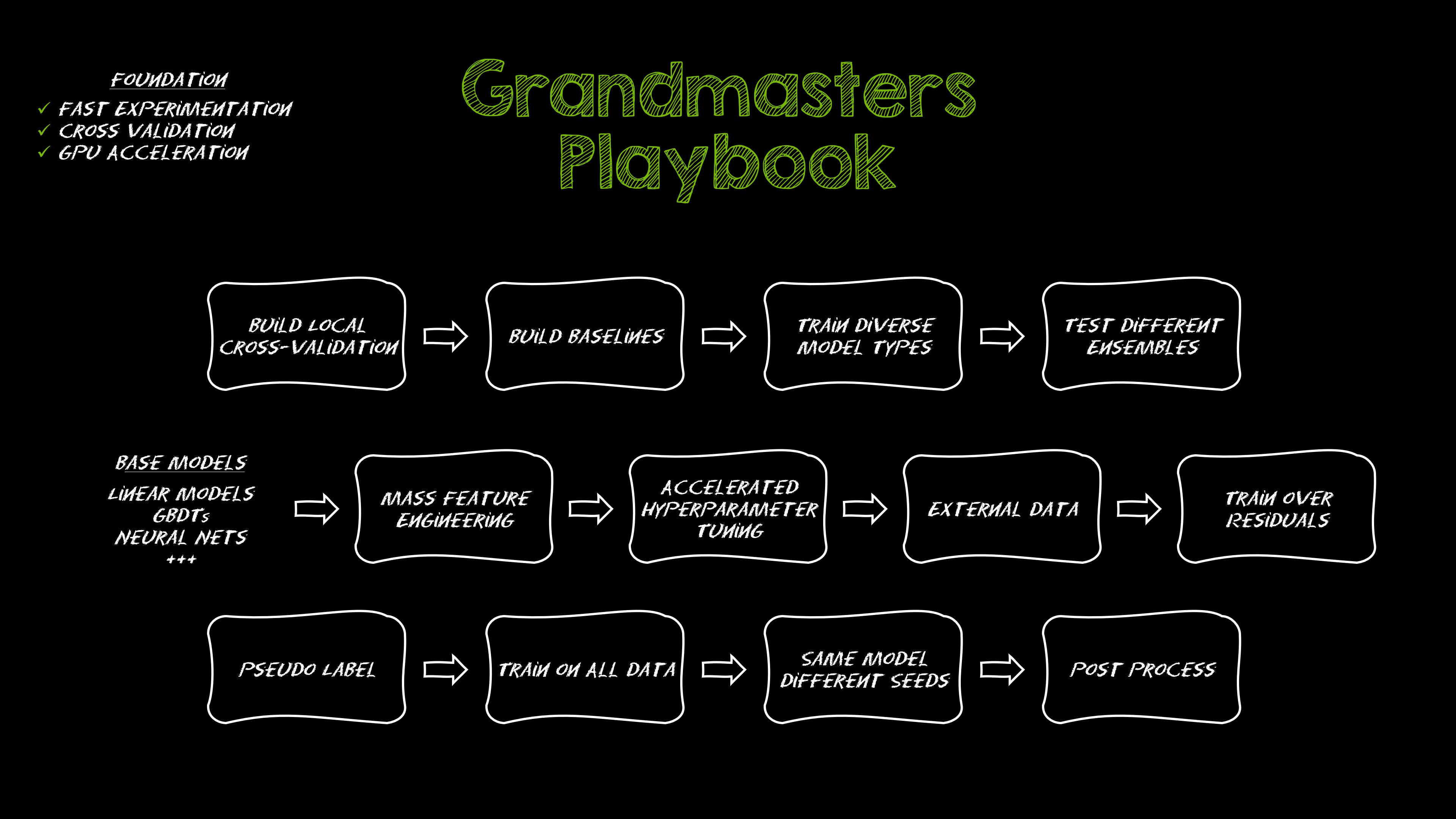

Manual de los Grandmasters de Kaggle: 7 Técnicas de Modelado para Datos Tabulares

Un análisis detallado de siete técnicas probadas por los Grandmasters de Kaggle para resolver rápidamente conjuntos de datos tabulares mediante aceleración por GPU, desde baselines variados hasta ensamblaje y pseudo-etiquetado.

NVIDIA RAPIDS 25.08 Agrega Nuevo profiler para cuML, Mejoras en el motor GPU de Polars y Soporte Ampliado de Algoritmos

RAPIDS 25.08 introduce perfiles de nivel de función y de línea para cuml.accel, el ejecutor de streaming por defecto del motor Polars GPU, soporte ampliado de tipos y cadenas, Spectral Embedding en cuML y aceleraciones de cero código para varios estimadores.