Cómo Meta mantiene confiable su hardware de IA

Sources: https://engineering.fb.com/2025/07/22/data-infrastructure/how-meta-keeps-its-ai-hardware-reliable, engineering.fb.com

TL;DR

- Meta opera una infraestructura de IA global con una gran cantidad de componentes de hardware, redes y almacenamiento, diseñada para entrenar modelos a gran escala y aplicaciones de IA. Cómo Meta mantiene confiable su hardware de IA

- Las fallas de hardware ocurren en discos, CPUs, memorias, conmutadores, GPUs, ASICs y redes, y más del 66% de las interrupciones de entrenamiento se deben a este tipo de fallas en clústeres grandes.

- Las corrupciones silenciosas de datos (SDC) son errores de cómputo sin trazas evidentes; ahora ocurren aproximadamente una falla por cada 1000 dispositivos.

- Meta utiliza mecanismos de detección a nivel de flota, incluidos los artículos «Detecting Silent Errors in the Wild» y «Hardware Sentinel», junto con telemetría y pruebas de estrés para prevenir, diagnosticar y recuperarse de fallas.

- La mitigación se divide en estrategias de infraestructura y de pila (stack), respaldando recuperaciones rápidas, triage de dispositivos y reinicios basados en puntos de control para minimizar el tiempo de inactividad durante el entrenamiento y la inferencia.

Contexto y antecedentes

La infraestructura global de IA de Meta comprende una gran cantidad de componentes de hardware y servidores, conectados por una red de malla en data centers distribuidos mundialmente. Esta configuración integra almacenamiento, cómputo y redes con sistemas de archivos únicos y aplicaciones de PyTorch orientadas a cargas de entrenamiento o inferencia. Esta infraestructura soporta el entrenamiento de modelos a gran escala y aplicaciones de IA avanzadas como la generación de texto a partir de imágenes y la segmentación de objetos. Desde 2018, el recorrido de fiabilidad de hardware de Meta ha llevado a hallazgos únicos sobre fallas en discos, CPUs, memorias, switches, GPUs, ASICs y redes, a menudo marcando la pauta en la identificación de modos de fallo. Se han desarrollado políticas de mitigación para garantizar operaciones fluidas y disponibilidad para miles de millones de usuarios y miles de casos internos. A medida que seguimos construyendo clústeres de IA de gran tamaño, comprender las fallas de hardware y las estrategias de mitigación es crucial para el entrenamiento fiable de modelos a gran escala. Entrenar modelos a gran escala implica miles de aceleradores en un entorno síncrono, donde cualquier fallo de un componente puede interrumpir el proceso. Meta se centra en reducir fallas de hardware durante el entrenamiento mediante detección y diagnóstico, y reinic iando el entrenamiento rápidamente con servidores y aceleradores sanos. Esto implica optimizar la categorización de fallas, triage de dispositivos, selección de nodos, validación de clústeres y restauración a partir de puntos de control. A partir de la experiencia con el conjunto de modelos Llama 3, las fallas de hardware en componentes como SRAM, HBMs, grids de procesamiento y hardware de conmutación de red impactan significativamente la fiabilidad de los clústeres de IA, con más del 66% de interrupciones de entrenamiento atribuibles a estas fallas. Los desafíos en clústeres de IA incluyen aceleradores que pueden ser menos confiables que las CPU debido a su complejidad y telemetría limitada; la complejidad de la red que podría resultar en fallas mal atribuidas; y errores en la pila de software de la GPU que pueden requerir configuraciones extensas para corregirse. Reducir fallas de hardware y de configuración mejora mucho la eficiencia del clúster. Las fallas de hardware observadas pueden clasificarse en tres categorías: fallas de hardware estáticas, errores transitorios y corrupciones silenciosas de datos (SDC). Las fallas estáticas aparecen como estados binarios: un dispositivo se enciende o se apaga. Estos errores son fáciles de identificar en flotas a gran escala. Si los dispositivos no se encienden o no se enumeran, verificaciones simples de salud pueden confirmar su presencia y configuraciones. A medida que crecen las configuraciones y la escala de los dispositivos en clústeres de entrenamiento, estas fallas ocurren con mayor frecuencia, pero son más fáciles de triage, localizar la causa y reparar, haciéndolas manejables a gran escala. Los errores transitorios se reproducen solo bajo ciertas condiciones e incluyen fallas dependientes de carga, problemas térmicos o fallos aleatorios no corregibles. La mitigación implica entender las condiciones de manifestación; y nuestra escala facilita el triage y la identificación de patrones, estableciendo trampas para estas condiciones cuando se producen. Los avances en telemetría de RAS en infraestructuras de gran escala han mejorado en gran medida este proceso. Factores como la sensibilidad a la carga de trabajo, el rango de temperatura, la frecuencia y parámetros de fabricación contribuyen a estas fallas. En algunos casos, se introducen cargas de trabajo artificiales en etapas no productivas para hacer que las fallas sean más repetibles. Capturar estados transitorios como valores de estado “pegajosos” proporciona indicios de fallas de hardware. Aunque son menos frecuentes que las fallas estáticas, la escala y el esfuerzo de ingeniería han hecho que estas situaciones sean detectables. Las corrupciones silenciosas de datos (SDC) ocurren cuando el hardware computa incorrectamente sin dejar trazas detectables, lo que lleva a que las aplicaciones consuman resultados incorrectos. Estas fallas pueden permanecer sin detectarse durante largos periodos si no se observan desviaciones significativas. Otros estudios, incluido un caso donde un error de cálculo provocó filas faltantes en una aplicación Spark, destacan la prevalencia de SDCs en infraestructuras de gran escala. Históricamente, las fallas relacionadas con errores suaves se redujeron a aproximadamente una por millón de dispositivos, pero con mayor densidad de silicio en aceleradores, las SDCs ocurren ahora alrededor de una por mil dispositivos. Las SDC presentan desafíos importantes en infraestructuras a gran escala debido a su dependencia de datos, haciendo inviable probar todo el espacio de valores posibles. También dependen de tensión, frecuencia, temperatura de operación y ciclo de vida del dispositivo; por ejemplo, un dispositivo puede fallar en verificaciones después de meses de uso, indicando desgaste. Por ello, se requieren pruebas consistentes, periódicas y frecuentes dentro de un espacio de estados aleatorio a lo largo de la vida útil del dispositivo para identificar estas imprecisiones. Para proteger las aplicaciones de las SDC, Meta utiliza varios mecanismos de detección descritos en los artículos Detecting Silent Errors in the Wild y Hardware Sentinel. En conjunto, estos tres mecanismos ofrecen una de las mejores coberturas en flota a escala para detectar y proteger nuestra infraestructura frente a SDC. Estas metodologías se ejecutan en toda la flota y están completamente producidas a gran escala, detectando SDC en infraestructuras de IA y no IA. En entrenamiento e inferencia, las SDC tienen implicaciones únicas: en entrenamiento, pueden llevar a cálculos erróneos en las pasadas hacia delante y hacia atrás, provocando divergencia en la trayectoria de entrenamiento. Aunque algunos entrenamientos son considerados auto-resilientes a SDCs, esto solo aplica a un subconjunto limitado de manifestaciones. Las SDC persisten a través de iteraciones, y la cuantificación de valores de datos en el entrenamiento aumenta la información por bit, exacerbando el impacto de las SDC y aumentando las tasas de divergencia. En inferencia, las SDC producen resultados incorrectos que pueden afectar a miles de consumidores; estas corrupciones pueden eludir políticas de privacidad o integridad. Depurar SDCs durante entrenamiento e inferencia es un reto complejo, que requiere telemetría extensa para identificar el nodo responsable. En entrenamiento, fallas visibles pueden detener el clúster, pero las SDC generan una ilusión de progreso y requieren identificar el nodo causante para evitar reinicios repetidos.

Lo nuevo

Meta detalla un enfoque maduro y a escala para detectar y mitigar SDC y otras fallas de hardware. Los métodos están totalmente desplegados y operan en toda la flota, con énfasis en reducir el tiempo de inactividad durante el entrenamiento y la inferencia. La organización subraya la importancia de entender las condiciones de manifestación, emparejar patrones a gran escala y hacer triage para identificar y aislar el hardware defectuoso. Los mecanismos de detección de SDC citados—los artículos Detecting Silent Errors in the Wild y Hardware Sentinel—constituyen la columna vertebral de la estrategia de detección de SDC a escala, permitiendo identificar y contener aceleradores y nodos defectuosos.

Por qué importa (impacto para desarrolladores/empresas)

Para desarrolladores y empresas, un hardware de IA confiable es fundamental para mantener el rendimiento y la fiabilidad de los servicios a gran escala. Entrenar modelos grandes requiere una infraestructura estable y tolerante a fallos; las fallas no detectadas pueden desperdiciar ciclos de computación, alargar el tiempo de entrenamiento y dificultar la depuración. La inferencia en pipelines que atienden millones de solicitudes depende de cálculos correctos para entregar resultados precisos; las SDC pueden degradar las salidas del modelo y, en el peor de los casos, violar la privacidad o la integridad. El enfoque de Meta—clasificación de fallas, telemetría y estrategias de detección y mitigación productivas—reducen interrupciones, aceleran la recuperación y mejoran la eficiencia general de los clústeres a medida que las cargas de trabajo se expanden a miles de aceleradores.

Detalles técnicos o Implementación

- Taxonomía de fallas: estáticas (encendido/apagado), transitorias (dependientes de carga, térmicas, intermitentes) y corrupciones silenciosas de datos (SDC).

- Detección y mitigación a gran escala: telemetría de flota, emparejamiento de patrones, trampas y pruebas; valores de estado “pegajosos” ayudan a capturar estados transitorios; cargas de trabajo artificiales en entornos no productivos facilitan hacer las fallas más repetibles para estudio.

- Mecanismos de detección de SDC: descritos en Detecting Silent Errors in the Wild y Hardware Sentinel, diseñados para proporcionar una cobertura sólida de SDC a gran escala.

- Consecuencias para entrenamiento e inferencia: las SDC pueden provocar propagación de NaN o variaciones de gradiente corruptas; en la inferencia, pueden producir resultados incorrectos para muchos usuarios.

- Respuesta práctica: cuando se detecta una falla, se aísla o mitiga el dispositivo o nodo defectuoso; el entrenamiento se reinicia con hardware sano y la inferencia se valida después de corregir la falla.

Conclusiones clave

- El programa de fiabilidad de hardware de Meta abarca fallas estáticas, transitorias y corrupciones silenciosas de datos, con flujos de detección y mitigación específicos.

- Las SDC son una preocupación creciente a escala y ocurren hoy aproximadamente una vez por mil dispositivos; requieren telemetría avanzada y pruebas rigurosas para su detección y mitigación.

- La combinación de estrategias de infraestructura y de pila, junto con mecanismos de detección productivos, apoya entrenamientos e inferencias fiables en miles de aceleradores.

- La propagación de NaN y la variación de gradiente corrupta son escenarios de divergencia de entrenamiento causados por SDC, que requieren identificación y aislamiento rápidos del hardware defectuoso.

- Datos reales de proyectos a gran escala, como Llama 3, ayudan a priorizar tipos de fallas y mejorar el triage, los puntos de control y las estrategias de reinicio.

Preguntas frecuentes

Referencias

More news

NVIDIA HGX B200 reduce la intensidad de las emisiones de carbono incorporado

El HGX B200 de NVIDIA reduce la intensidad de carbono incorporado en un 24% frente al HGX H100, al tiempo que ofrece mayor rendimiento de IA y eficiencia energética. Este artículo resume los datos PCF y las novedades de hardware.

Cómo reducir cuellos de botella KV Cache con NVIDIA Dynamo

NVIDIA Dynamo offloads KV Cache desde la memoria de la GPU hacia almacenamiento económico, habilitando contextos más largos, mayor concurrencia y costos de inferencia más bajos para grandes modelos y cargas de IA generativa.

Microsoft transforma el sitio de Foxconn en el data center Fairwater AI, descrito como el más poderoso del mundo

Microsoft anuncia planes para un data center Fairwater AI de 1,2 millones de pies cuadrados en Wisconsin, con cientos de miles de GPU Nvidia GB200. El proyecto de 3.3 mil millones de dólares promete un entrenamiento de IA sin precedentes.

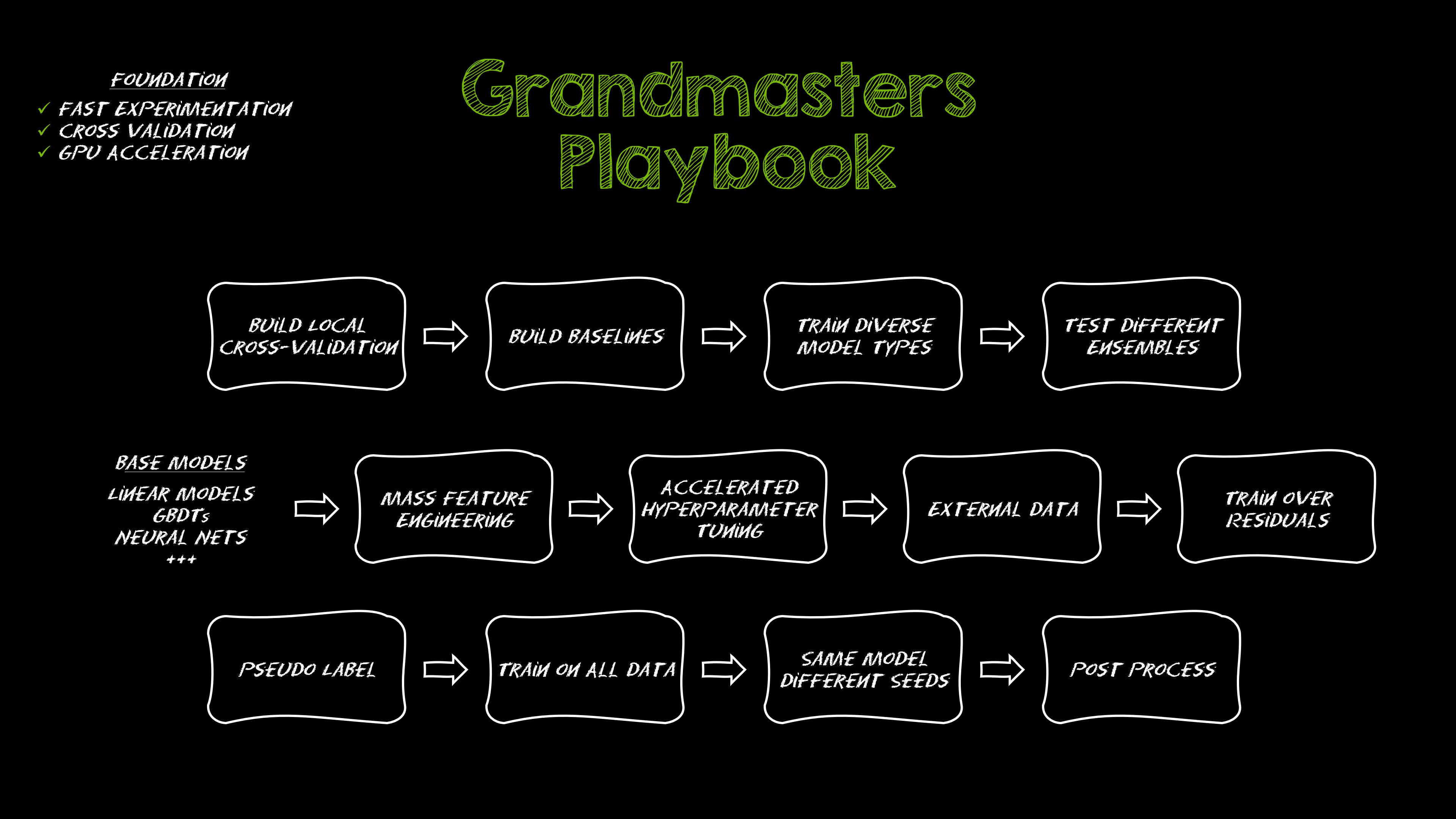

Manual de los Grandmasters de Kaggle: 7 Técnicas de Modelado para Datos Tabulares

Un análisis detallado de siete técnicas probadas por los Grandmasters de Kaggle para resolver rápidamente conjuntos de datos tabulares mediante aceleración por GPU, desde baselines variados hasta ensamblaje y pseudo-etiquetado.

NVIDIA RAPIDS 25.08 Agrega Nuevo profiler para cuML, Mejoras en el motor GPU de Polars y Soporte Ampliado de Algoritmos

RAPIDS 25.08 introduce perfiles de nivel de función y de línea para cuml.accel, el ejecutor de streaming por defecto del motor Polars GPU, soporte ampliado de tipos y cadenas, Spectral Embedding en cuML y aceleraciones de cero código para varios estimadores.

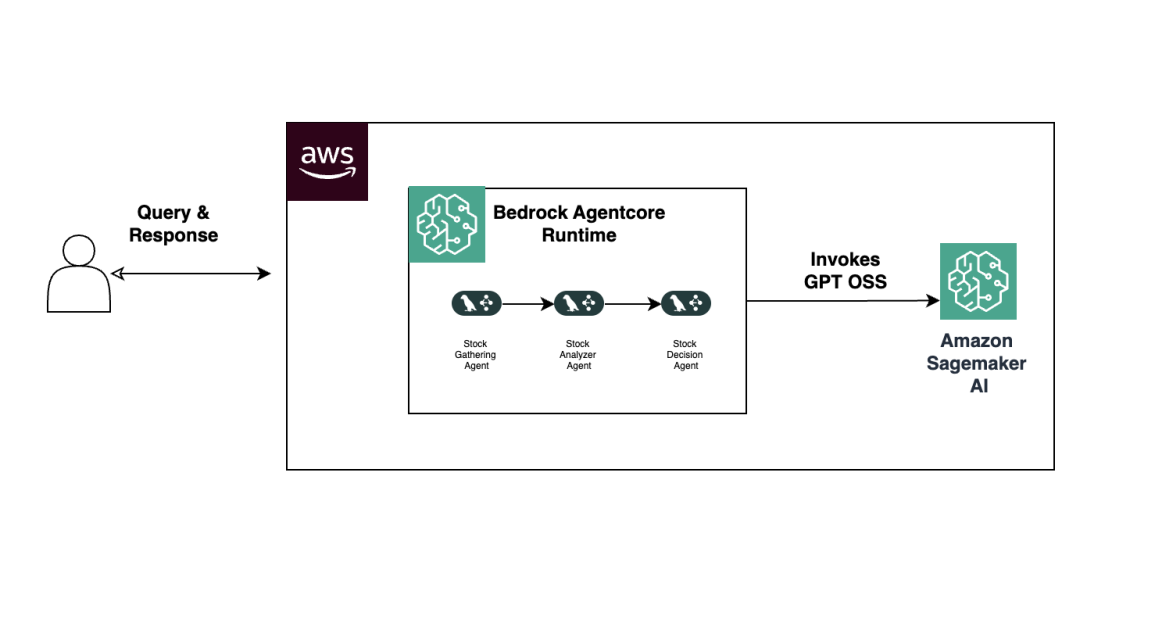

Construir Flujos de Trabajo Agenticos con GPT OSS de OpenAI en SageMaker AI y Bedrock AgentCore

Visión general de extremo a extremo para implementar modelos GPT OSS de OpenAI en SageMaker AI y Bedrock AgentCore, impulsando un analizador de acciones multiagente con LangGraph, con cuantización MXFP4 de 4 bits y orquestación serverless.