CUDA Toolkit 13.0: Tile programming, unified Arm support, and faster builds

Sources: https://developer.nvidia.com/blog/whats-new-and-important-in-cuda-toolkit-13-0, developer.nvidia.com

TL;DR

- CUDA Toolkit 13.0 is a major release that lays groundwork for future CUDA 13.X developments, with new tile-based programming and cross-Arm unification across server and embedded devices.

- The tile programming model provides a high-level abstraction that maps to Tensor Cores and is designed for forward compatibility across current and future GPUs.

- NVIDIA unified the CUDA toolkit across Arm SBSA servers and embedded platforms (except Orin, sm_87), enabling a single install for simulation, testing, and deployment.

- Nsight Compute 2025.3 adds deeper source-level analysis (Instruction Mix, Scoreboard Dependency) and a Throughput Breakdown view to diagnose bottlenecks.

- The default fatbin compression scheme switches to Zstandard (ZSTD) for better compression; decompression-time options remain available, with further size reductions seen in CUDA Math APIs. For more details, see the original NVIDIA post announcing these changes.

Context and background

CUDA has long relied on a thread-parallel SIMT execution model. CUDA 13.0 advances this foundation by introducing a tile-based programming model, aiming to complement SIMT with a higher-level approach that can simplify large-scale data operations while preserving full GPU performance. This shift occurs in the broader context of ongoing hardware evolution, including NVIDIA’s Blackwell architecture and its continued improvements across the GPU lineup. As a major release, CUDA 13.0 also acts as the foundation for the rest of the CUDA 13.X software lineup, signaling a long-term direction for developer productivity and hardware efficiency. NVIDIA has highlighted that the tile model is designed to map naturally onto Tensor Cores, and the compiler will handle memory management and operation mapping for these tiles, enabling developers to focus more on algorithms and performance outcomes rather than low-level thread management. The company also discussed a broader move to unify toolchains across Arm-based servers and embedded devices, a change that can shorten the path from simulation to deployment across diverse platforms. The consolidation of toolchains has practical implications for workflows that span SBSA servers (Grace-based systems, Arm workstations, etc.) and embedded devices (Jetson, Thor, and others). Historically, development for SBSA and embedded platforms involved separate toolchains, sysroots, libraries, and container images. CUDA 13.0 introduces a single toolkit that applies across targets, allowing developers to build once and deploy to both servers and embedded targets by selecting the appropriate compute architecture (e.g., sm_XX). This reduces duplication in CI pipelines and simplifies container management, while maintaining performance and flexibility. The change is designed to improve productivity and reduce the overhead of maintaining separate SDKs and build ecosystems. At the software ecosystem level, NVIDIA is also consolidating image and container lineage to support unified simulation, testing, and deployment workflows, further blurring the lines between development, simulation, and real hardware deployment. This unification is presented as a major productivity boost with no sacrifice in performance, enabling teams to move faster from algorithm design to deployment on evolving GPUs and architectures. NVIDIA also notes that CUDA Toolkit 13.0 has been qualified against new operating system targets, though the full support matrix is documented in release notes and Installation Guides.

What’s new

Tile-based programming model and forward compatibility

CUDA 13.0 introduces the groundwork for a tile (array) programming model that complements the traditional SIMT approach. In this model, developers define tiles of data and specify operations over those tiles, while the compiler and runtime distribute work across threads and optimize hardware usage. This abstraction frees developers from managing low-level thread behavior while preserving the ability to extract full GPU performance. Key aspects of tile programming as described by NVIDIA include:

- A high-level abstraction designed to map naturally to Tensor Cores.

- A compiler-driven memory management and operation mapping for tiles, reducing manual optimization effort.

- Forward compatibility: code written today can run efficiently on current GPUs and future generations without rewriting algorithms.

- An indication that tile programming will become available at multiple levels, with CUDA 13.0 introducing low-level infrastructure to support the model and paving the way for higher-level usage in the future. This is positioned as a major step toward combining ease of use with maximum performance and long-term portability on NVIDIA hardware.

Unified CUDA toolkit across Arm SBSA servers and embedded devices

A central focus of CUDA 13.0 is unifying the toolkit for Arm-based platforms. The goal is to remove the need for separate installations and toolchains for SBSA-compliant servers and embedded systems (e.g., Thor), enabling a single CUDA install to support all Arm targets. Orin (sm_87) will continue on its current path for now. What this means in practice:

- Build, test, and deploy a robotics or AI application with the same binary across simulation on high-performance systems and deployment on embedded targets.

- Eliminate the need for two separate toolchains, reducing duplication, CI overhead, and the risk of version mismatches.

- Use a single compiler, headers, and libraries across targets; switching is a matter of selecting the appropriate compute architecture (sm_XX).

- Extend to containers, enabling consistent image lineage across simulation, testing, and deployment workflows with fewer rebuilds and smoother transitions from code to hardware. NVIDIA describes this unification as a major productivity boost for developers and organizations alike, reducing engineering time spent on infrastructure and enabling teams to focus on algorithms, performance, and deployment.

Nsight Compute 2025.3 enhancements

InNsight Compute 2025.3, NVIDIA adds enhanced analysis capabilities to the source view: Instruction Mix and Scoreboard Dependency tables enable users to pinpoint source lines affected by long dependency stalls and to identify input/output dependency locations more efficiently. A new Throughput Breakdown section in the Metric Details window provides per-unit throughput metrics, helping users see where throughput may bottleneck. These enhancements are designed to make performance debugging more precise and accessible, especially for developers optimizing complex kernels where dependency stalls can limit overall throughput.

Fatbins, compression defaults, and library size optimizations

CUDA 13.0 changes the default compression scheme for fatbins to use Zstandard (ZSTD), a modern compression algorithm with better ratios than the previous default. Fatbins, which store multiple architecture-specific code variants (e.g., sm_89, sm_100), are compressed during compilation to reduce binary size. The compression choice made by the —compress-mode option remains compatible with all drivers that support 13.x toolkits, and the default change aligns with the goal of better compression without measurable slowdown. Specific examples from NVIDIA’s testing include notable size reductions in the CUDA Math APIs and other libraries:

- CUDA Math APIs show a 17% size reduction with the new default compression.

- Under a size-focused compress-mode, even larger reductions are possible, with demonstrations like CUDA Math APIs achieving up to a 71% reduction.

- Decompression time remains a factor for some applications, so the options to favor speed (—compress-mode=none or —no-compress) remain available. NVIDIA notes that there were no overall library-level regressions in execution time with the new defaults, and that some applications can realize substantial size reductions without sacrificing performance.

Other implementation notes

CUDA 13.0 continues to rely on a unified toolchain concept, with changes in NVCC, NVC++, fatbinary, and nvFatbin that propagate to the compiler and runtime. The aim is to provide a single, portable toolchain that can produce optimized code for the target GPU architecture while simplifying cross-platform development and deployment. The CUDA core remains a key component of the CUDA ecosystem, including the cuda.core module mentioned within the CUDA Python ecosystem as a bridge to Pythonic access to CUDA functionality. This reinforces the broader trend of making CUDA development more accessible while preserving low-level performance characteristics.

Why this matters for developers and enterprises

- Productivity gains: A unified toolkit across Arm servers and embedded platforms reduces duplication, minimizes CI overhead, and lowers maintenance complexity for cross-target projects.

- Forward compatibility: Tile programming, together with the Tensor Core alignment and compiler-driven optimization, helps ensure today’s code remains efficient on future GPUs.

- Deployment simplification: A single binary path from simulation to deployment reduces the risk of version mismatches and accelerates the path from model development to real-world execution.

- Performance consistency: Even with higher-level abstractions, the compiler and runtime continue to generate optimized code for the target architecture, so developers do not compromise on performance.

Technical details or implementation notes

- Tile programming is designed to map cleanly onto Tensor Cores, with the compiler handling tile memory management and operation mapping.

- The unified Arm toolkit enables building for SBSA servers and embedded targets without multiple toolchains, containers, or sysroots.

- The default fatbin compression now uses Zstandard, with options for speed-focused compression and a none/no-compress mode to control decompression times.

- Nsight Compute 2025.3 adds improved source-level insights, including Instruction Mix and Scoreboard Dependency analyses, plus a Throughput Breakdown view.

- Orin remains on its current path; other Arm architectures are supported under the unified toolchain.

Key takeaways

- Tile-based programming is introduced as a major new model that complements SIMT and maps to Tensor Cores, with forward compatibility across GPUs.

- CUDA Toolkit 13.0 unifies the toolchain for Arm SBSA servers and embedded platforms under a single CUDA install, simplifying development and deployment.

- Nsight Compute 2025.3 enhancements provide deeper, more actionable performance diagnostics at the source level.

- The default fatbin compression switches to Zstandard, delivering meaningful binary-size reductions without runtime penalties in most cases.

- The change to a unified toolchain and container lineage reduces CI overhead and accelerates the path from code to hardware, while preserving performance.

FAQ

-

What is tile-based programming in CUDA 13.0?

It is a higher-level programming model where developers define tiles of data and operations; the compiler and runtime distribute work and optimize hardware usage, mapping onto Tensor Cores for performance, while maintaining forward compatibility with future GPUs.

-

How does the Arm unification affect my projects?

You can build once with a single CUDA toolkit and deploy to both SBSA servers and embedded platforms (except Orin) by choosing the correct compute architecture, reducing duplication and CI overhead.

-

What changed with fatbin compression?

The default compression scheme now uses Zstandard, improving compression ratios with negligible execution-time impact; there are still options to favor decompression speed or extreme size reductions as needed.

-

What are the Nsight Compute 2025.3 improvements?

It adds Instruction Mix and Scoreboard Dependency tables in the source view and a new Throughput Breakdown section, helping pinpoint bottlenecks and inefficiencies at the source level.

-

Is Orin supported under the unified toolkit?

Orin (sm_87) will continue on its current path for now, while other Arm SBSA and embedded targets are supported by the unified CUDA toolkit.

References

More news

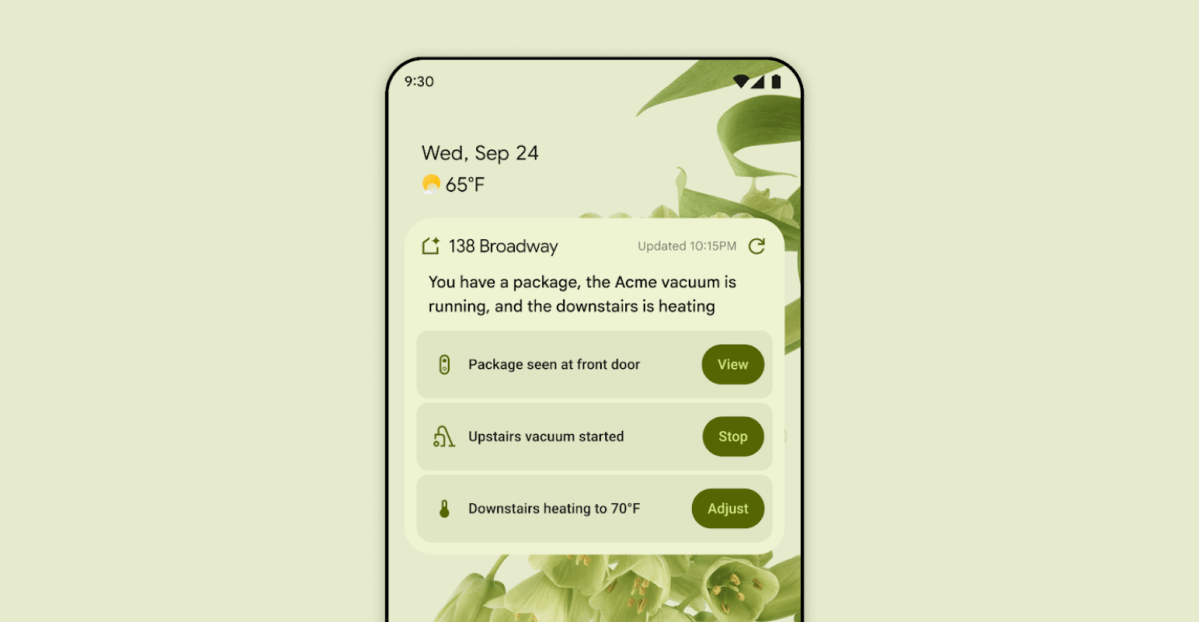

First look at the Google Home app powered by Gemini

The Verge reports Google is updating the Google Home app to bring Gemini features, including an Ask Home search bar, a redesigned UI, and Gemini-driven controls for the home.

NVIDIA HGX B200 Reduces Embodied Carbon Emissions Intensity

NVIDIA HGX B200 lowers embodied carbon intensity by 24% vs. HGX H100, while delivering higher AI performance and energy efficiency. This article reviews the PCF-backed improvements, new hardware features, and implications for developers and enterprises.

OpenAI reportedly developing smart speaker, glasses, voice recorder, and pin with Jony Ive

OpenAI is reportedly exploring a family of AI devices with Apple's former design chief Jony Ive, including a screen-free smart speaker, smart glasses, a voice recorder, and a wearable pin, with release targeted for late 2026 or early 2027. The Information cites sources with direct knowledge.

Shadow Leak shows how ChatGPT agents can exfiltrate Gmail data via prompt injection

Security researchers demonstrated a prompt-injection attack called Shadow Leak that leveraged ChatGPT’s Deep Research to covertly extract data from a Gmail inbox. OpenAI patched the flaw; the case highlights risks of agentic AI.

Predict Extreme Weather in Minutes Without a Supercomputer: Huge Ensembles (HENS)

NVIDIA and Berkeley Lab unveil Huge Ensembles (HENS), an open-source AI tool that forecasts low-likelihood, high-impact weather events using 27,000 years of data, with ready-to-run options.

Scaleway Joins Hugging Face Inference Providers for Serverless, Low-Latency Inference

Scaleway is now a supported Inference Provider on the Hugging Face Hub, enabling serverless inference directly on model pages with JS and Python SDKs. Access popular open-weight models and enjoy scalable, low-latency AI workflows.