CUDA Pro Tip: Increase Performance with Vectorized Memory Access

Sources: https://developer.nvidia.com/blog/cuda-pro-tip-increase-performance-with-vectorized-memory-access, developer.nvidia.com

TL;DR

- Vectorized loads and stores can increase bandwidth utilization while reducing the number of executed instructions.

- Use CUDA C++ vector data types (e.g., int2, int4, float2, float4) to create 64- or 128-bit wide memory operations.

- Alignment is essential: misaligned offsets invalidate vectorized loads; use properly aligned offsets (e.g., reinterpret_cast (d_in+2)).

- Vectorization can reduce instruction counts by up to 2x (vector2) or 4x (vector4) but may increase register pressure or reduce parallelism in some kernels.

Context and background

Many CUDA kernels are bandwidth bound. As newer hardware increases the flops-to-bandwidth ratio, more kernels become bandwidth bound, underscoring the need to mitigate memory bottlenecks in code. CUDA Pro Tip articles emphasize practical techniques to improve throughput by better utilizing memory bandwidth. In this discussion, vector loads and stores are explored as a straightforward, low-friction optimization to enhance bandwidth utilization and lower instruction counts. A simple memory copy kernel provides a concrete example. The kernel uses grid-stride loops to traverse global memory. By inspecting the assembly (SASS) produced for the scalar copy kernel, one observes LDG.E and STG.E instructions that load and store 32-bit values from and to global memory. This baseline can be improved by switching to vectorized loads and stores that operate on wider data widths. The goal is to reduce the number of instructions and improve memory bandwidth throughput as the copy size grows. The analysis of the SASS and the related performance figures are part of the broader CUDA toolkit workflow, including the cuobjdump tool used to inspect generated code. NVIDIA CUDA Pro Tip: Increase Performance with Vectorized Memory Access. The essential idea is simple: load and store more data per instruction by using 64-bit or 128-bit wide memory operations rather than the default 32-bit operations. This reduces instruction count and latency while boosting effective bandwidth utilization. In practice, you can drive this by using vector data types and careful casting so the compiler emits the wider vectorized instructions.

What’s new

The post demonstrates several concrete changes to a memory copy kernel to adopt vectorized loads:

- The loop is restructured to process two elements per iteration, so it runs N/2 times. This inherently halves the number of iterations and, when combined with wider loads, reduces instruction count.

- Casting is used to reinterpret memory pointers as vector types. For example, a pointer to int is cast to an int2 pointer (e.g.,

reinterpret_cast (d_in)), so dereferencing yields a pair of ints treated as a single unit. In C, a similar approach can be expressed as a cast like(int2*(d_in)). This approach makes the compiler emit vectorized instructions such asLDG.E.64andSTG.E.64. - A follow-on version uses 128-bit wide vectors (int4/float4) so the compiler emits

LDG.E.128andSTG.E.128. In those versions, the overall instruction count is reduced further—up to a 4x reduction for a vector4 copy compared with the scalar version. - You launch half as many threads as in the scalar kernel when using vectorized loads of two elements per iteration, which contributes to the performance gains.

- The broader performance picture shows that, for most workloads, vectorized loads outperform scalar loads because they increase bandwidth, reduce instruction count, and reduce latency. However, vectorization comes with caveats: it can increase register pressure and potentially reduce parallelism. If a kernel is already register-bound or has very low parallelism, scalar loads may remain the better choice. There are also alignment constraints: data must be aligned, and data type sizes must be powers of two for vectorized loads to be valid. If those conditions are not met, vectorized loads cannot be used. These observations are summarized in practical terms: vectorized memory access is a fundamental CUDA optimization you should use when possible, because it improves bandwidth efficiency and reduces latency with relatively small changes to existing kernels. The blog notes that the techniques have been updated to reflect behavior on current GPUs.

Why it matters (impact for developers/enterprises)

For developers building CUDA kernels, improving memory bandwidth utilization translates directly into higher effective throughput for data-heavy pipelines. Bandwidth-bound kernels disproportionately benefit from vectorized memory access, because fewer instructions are needed to move the same amount of data, and the data can be streamed more efficiently from global memory. Enterprises running compute workloads on CUDA-enabled hardware can achieve better utilization of their GPU resources by adopting broader vectorization where alignment and data-type constraints permit. The approach can reduce total instruction counts and, in turn, reduce energy usage per data unit moved. The general guidance is to weigh the benefits of reduced instruction count against the risk of higher register pressure and to evaluate whether the kernel’s parallelism is sufficient to absorb the change.

Technical details or Implementation (how to apply it)

Below is a distilled guide drawn from the CUDA Pro Tip content on vectorized memory access. It outlines practical steps to convert a scalar memory copy to a vectorized version and highlights the key caveats.

- Start from a simple memory copy kernel that uses scalar loads and stores. Use grid-stride loops as described in earlier CUDA Pro Tip posts to traverse memory.

- Replace 32-bit scalar loads with 64-bit wide vector loads where possible:

- Use vector data types defined in CUDA C++ headers, such as

int2,int4,float2, orfloat4. These types represent multiple values packed into a single data unit. - Cast the input pointer to a vector type, for example:

reinterpret_cast (d_in). Dereferencing such a pointer yields a vector, and the compiler will generate vectorized instructions. - Be mindful of alignment. Device-allocated memory is automatically aligned to the size of the data type, but any offset must itself be aligned to the vector’s size. For example,

reinterpret_cast (d_in+1)is invalid becaused_in+1is not aligned tosizeof(int2). A safe offset would bereinterpret_cast (d_in+2). - For broader vector widths, you can use a 128-bit vector, such as

int4/float4. The corresponding SASS will emitLDG.E.128andSTG.E.128instructions. This version can reduce the instruction count by a factor of four relative to the scalar version, depending on the kernel and data layout. - When you switch to vectorized loads, you effectively process more data per iteration. The loop can be adjusted to execute half as many iterations (N/2) and, correspondingly, you can launch half as many threads as in the scalar kernel.

- There is a non-trivial trade-off to consider: while vectorized loads boost bandwidth and reduce instruction counts, they can increase register pressure and reduce parallelism. If a kernel is already constrained by registers or if its parallelism is low, sticking to scalar loads may yield better performance.

- Data alignment and type size constraints matter. Vectorized loads require aligned data and data type sizes that are powers of two. If either condition is not met, vectorized loads cannot be used.

- To validate changes, tools such as cuobjdump (for inspecting the generated SASS) can be used to confirm the presence of vectorized instructions like

LDG.E.64,STG.E.64,LDG.E.128, andSTG.E.128.

Key implementation notes and caveats

- The ability to use vectorized loads hinges on data alignment. Misaligned offsets invalidate vectorized loads. Use aligned offsets when offsetting pointers from the base, as in the aligned example above.

- The structure size used for vectorization should be a power of two bytes to avoid padding issues and to ensure efficient alignment on typical architectures.

- Vectorization is not a universal optimization. If your kernel has heavy register pressure or poor parallelism, scalar loads may achieve better overall performance.

Key takeaways

- Vectorized memory access can significantly improve bandwidth utilization and reduce instruction counts in CUDA kernels.

- The simplest path to vectorization is to use vector data types (

int2,int4,float2,float4) by reinterpreting pointers, ensuring proper alignment and power-of-two data sizes. - A two-element vector (vector2) can yield about a 2x improvement in instruction count; a four-element vector (vector4) can yield up to a 4x reduction in instruction count compared with scalar loads.

- Vectorized loads may increase register pressure and reduce parallelism, so evaluate kernels carefully. If a kernel is register-bound or has limited parallelism, scalar loads may be the better choice.

- The technique is a practical, low-friction optimization that can be added with only a few changes to existing kernels, and it has been updated to reflect behavior on current GPUs.

FAQ

-

Do vectorized loads always improve performance?

Generally they improve bandwidth utilization and reduce instruction counts, but they can increase register pressure and reduce parallelism. If a kernel is register-bound or has low parallelism, scalar loads may perform better.

-

What are the alignment requirements?

Data must be aligned to the size of the vector type. Offsets must be aligned; e.g., `reinterpret_cast (d_in+2)` is valid, while `reinterpret_cast (d_in+1)` is not.

-

Which data types can be vectorized in CUDA C++?

Vector data types such as `int2`, `int4`, `float2`, and `float4` can be used to implement vectorized loads.

-

Can vectorization be applied to any kernel?

Vectorization is not guaranteed to help every kernel. It requires data alignment and data-type sizes that are powers of two, and kernel characteristics (e.g., register pressure, parallelism) must be favorable.

-

How can I verify that vectorized instructions are emitted?

Tools like cuobjdump can inspect the SASS to confirm the presence of vectorized instructions such as `LDG.E.64`/`STG.E.64` and `LDG.E.128`/`STG.E.128`.

References

- NVIDIA CUDA Pro Tip: Increase Performance with Vectorized Memory Access — https://developer.nvidia.com/blog/cuda-pro-tip-increase-performance-with-vectorized-memory-access

More news

NVIDIA HGX B200 Reduces Embodied Carbon Emissions Intensity

NVIDIA HGX B200 lowers embodied carbon intensity by 24% vs. HGX H100, while delivering higher AI performance and energy efficiency. This article reviews the PCF-backed improvements, new hardware features, and implications for developers and enterprises.

Predict Extreme Weather in Minutes Without a Supercomputer: Huge Ensembles (HENS)

NVIDIA and Berkeley Lab unveil Huge Ensembles (HENS), an open-source AI tool that forecasts low-likelihood, high-impact weather events using 27,000 years of data, with ready-to-run options.

How to Reduce KV Cache Bottlenecks with NVIDIA Dynamo

NVIDIA Dynamo offloads KV Cache from GPU memory to cost-efficient storage, enabling longer context windows, higher concurrency, and lower inference costs for large-scale LLMs and generative AI workloads.

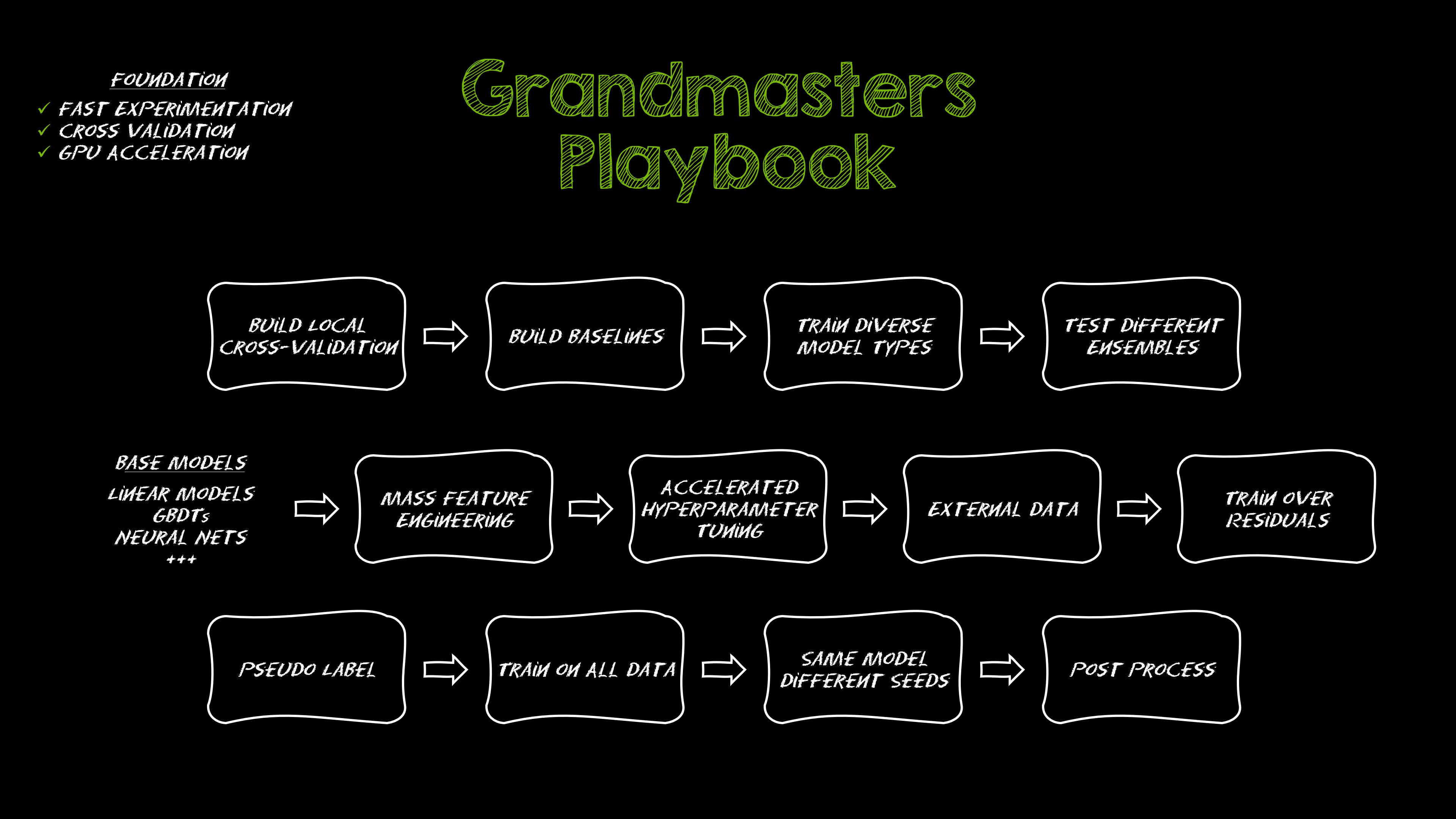

Kaggle Grandmasters Playbook: 7 Battle-Tested Techniques for Tabular Data Modeling

A detailed look at seven battle-tested techniques used by Kaggle Grandmasters to solve large tabular datasets fast with GPU acceleration, from diversified baselines to advanced ensembling and pseudo-labeling.

Speculative Decoding to Reduce Latency in AI Inference: EAGLE-3, MTP, and Draft-Target Approaches

A detailed look at speculative decoding for AI inference, including draft-target and EAGLE-3 methods, how they reduce latency, and how to deploy on NVIDIA GPUs with TensorRT.

NVIDIA RAPIDS 25.08 Adds New Profiler for cuML, Polars GPU Engine Enhancements, and Expanded Algorithm Support

RAPIDS 25.08 introduces a function- and line-level profiler for cuml.accel, a default streaming executor for the Polars GPU engine, expanded datatype and string support, a new Spectral Embedding algorithm in cuML, and zero-code-change accelerations for several estimators.